He creado esta entrada para que pensemos cómo podemos utilizar RCSG y covergroups en la verificación de un microprocesador. Una forma que se me ocurre de hacerlo (y desde luego no es única) es la que os voy a describir. Es el momento adecuado porque empezamos esta semana a conocer el código máquina de los diferentes tipos de instrucciones del…

-

-

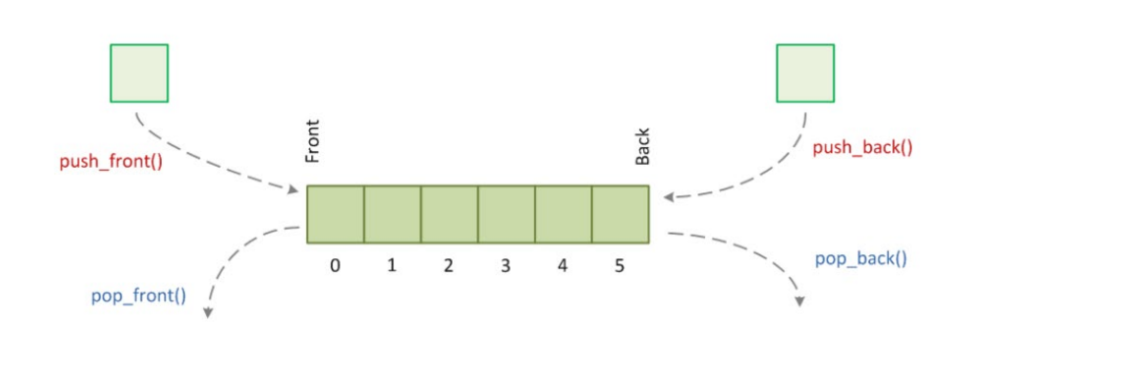

Modelo de Fifo ideal con colas

En este enlace podréis ver una modelización de una fifo como la solicitada en la tarea 1 mediante una cola y un pequeño banco de pruebas de algunos casos de verificación. Paso de argumentos por referencia siempre teniendo en cuenta que el paso no puede ser por valor sino por referencia (por eso se utiliza la palabra reservada ref). Si…