ROM Asíncronas

- Cambian el puerto de salida cuando cambia la dirección de lectura sin la necesidad de un flanco de reloj adicional

- La inferencia de memorias asíncronas depende de la tecnología que se dispone. En la actualidad la mayoría de las memorias embebidas de los dispositivos programables son síncronas y esta inferencia de memorias asíncronas (combinacionales sin reloj) deriva en una implementación realizada con lógica (LUTs)

module rom_asynch (address,dout);

parameter d_width = 16;

parameter a_width = 6;

input [a_width-1:0] address;

output [d_width-1:0] dout;

logic [d_width-1:0] mem[(1<<a_width)-1:0] ;

initial

$readmemh("pesos_2.dat", mem);

assign dout = mem[address];

endmodule

ROM Síncronas

- Cambian el puerto de salida cuando cambia la dirección de lectura siempre y cuando tengamos un flanco de reloj

- La inferencia de memorias síncronas es directa en memorias embebidas. Por ejemplo en un dispositivo como la Cyclone IV del laboratorio sería mediante las memorias embebidas de 9kbits

module rom_synch_in

#(parameter DATA_WIDTH=32, parameter ADDR_WIDTH=7)

(

input [(ADDR_WIDTH-1):0] addr,

input clk,

output logic [(DATA_WIDTH-1):0] q

);

// Declare the ROM variable

logic [DATA_WIDTH-1:0] rom[2**ADDR_WIDTH-1:0];

initial

begin

$readmemh("tanh_1.dat", rom);

end

always_ff @ (posedge clk)

begin

q <= rom[addr];

end

endmodule

module rom_synch_in

#(parameter DATA_WIDTH=32, parameter ADDR_WIDTH=7)

(

input [(ADDR_WIDTH-1):0] addr,

input clk,

output logic [(DATA_WIDTH-1):0] q

);

// Declare the ROM variable

logic [DATA_WIDTH-1:0] rom[2**ADDR_WIDTH-1:0];

initial

begin

$readmemh("tanh_1.dat", rom);

end

always_ff @ (posedge clk)

begin

q <= rom[addr];

end

endmodule

Inicialización de las ROM

Para aportar contenidos a la memoria utilizaremos “system tasks” preestablecidos

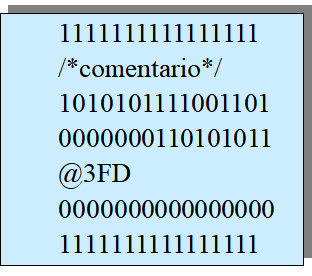

- $readmemb: Obtiene los contenidos de un fichero ASCII en donde los valores están escritos en formato binario

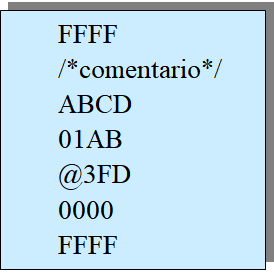

- $readmemh: Obtiene los contenidos de un fichero ASCII en donde los valores están escritos en formato hexadecimal

- Cuando se desea introducir una dirección, el formato utilizado es en hexadecimal en cualquiera de los casos .

- Suele llamarse a dichos procedimientos desde un initial como se ha visto en los ejemplos anteriores

- Aunque el fichero puede tener una extensión básica de .txt, es recomendable la utilización de la extensión .dat

La sintaxis completa de este tipo de «system task» es:

$readmemb(“<file_name>”, <memory_name>, <start_addr>?,<finish_addr>?);

siendo los dos últimos argumentos opcionales