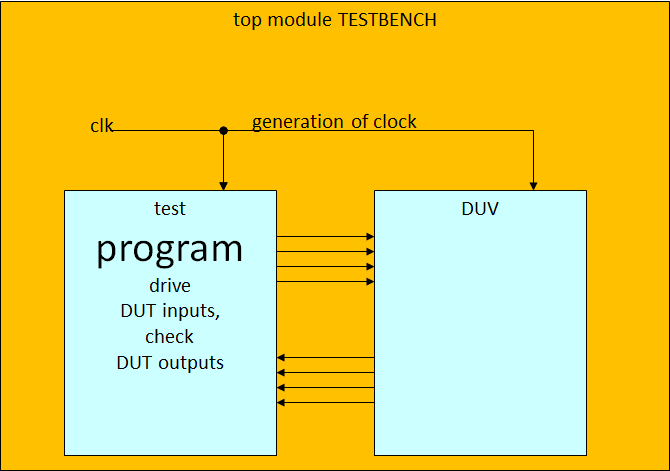

Estamos ante una construcción que pretendía en su creación que aglutinara todas las estructuras de test que necesitáramos para controlar los estimulos a introducir a un DUV y para observar los resultados del DUV.

El “ test” (program) corre separadamente del diseño (module)

- Disparado por el reloj

- Muestrea las salidas del DUV justo antes del flanco activo de reloj y

- Conduce las entradas del DUV justo después de dicho flanco

Programs SON COMO MÓDULOS, pero:

- No pueden contener always

- No pueden incluir módulos

- La simulación finaliza automáticamente cuando todos los estamentos del initial se han completado

- Normalmente define un «test» con comportamiento libre de carreras

- Definición de estímulos

- Elementos de verificación

- No permite comportamiento concurrente

- Puede ser instanciado en un testbench como si de un módulo se tratara

Los programas pueden hacer todo lo necesario para la verificación, con lo cual hablaremos de ellos de nuevo cuando planteemos una arquitectura de testbench… pero veamos un pequeño ejemplo