- Es la incorporación más relevante del systemVerilog a la descripción estructural

- La idea original parece que intenta solucionar los temas de interconexión complejos cuando se manejan muchos puertos en las módulos que se están interconectando. Así por ejemplo cuando se realiza la interconexión de un sistema digital basado en un determinado bus de interconexión( interconectando microprocesadores y periféricos varios) la realización mediante puertos individuales es una solución posible pero muy dada a errores conforme la complejidad aumenta.

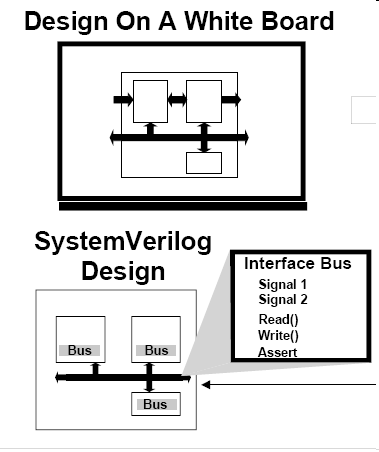

- Entonces se pensó en un encapsulamiento de toda la interconexión y las funcionalidades de comunicación derivadas de esas interconexiones en una nueva construcción que denominaron «interfaz»

- Es difícil encontrarle un claro precursor

- Es algo más que una entidad de VHDL

- Es bastante diferente a los interfaces de Vera pero hereda

- la idea que subyace en Virtual Ports & Binds de Vera

Por tanto tenemos una nueva construcción, específicamente diseñado para jerarquía que

- Encapsula la interconexión y comunicación

- Separa la comunicación de la funcionalidad

- Funcionalidad (assertions y rutinas)

- Habilita la abstracción en una descripción RTL (conexión mediante interfaces)

- Puede incluir información de dirección pero incluyendo los diferentes puntos de vista de los elementos interconectados (modports)

- Master-Slave

- Transmisor-Receptor

- Test-DUV

- y puede incluir elementos de sincronización: (clocking blocks)