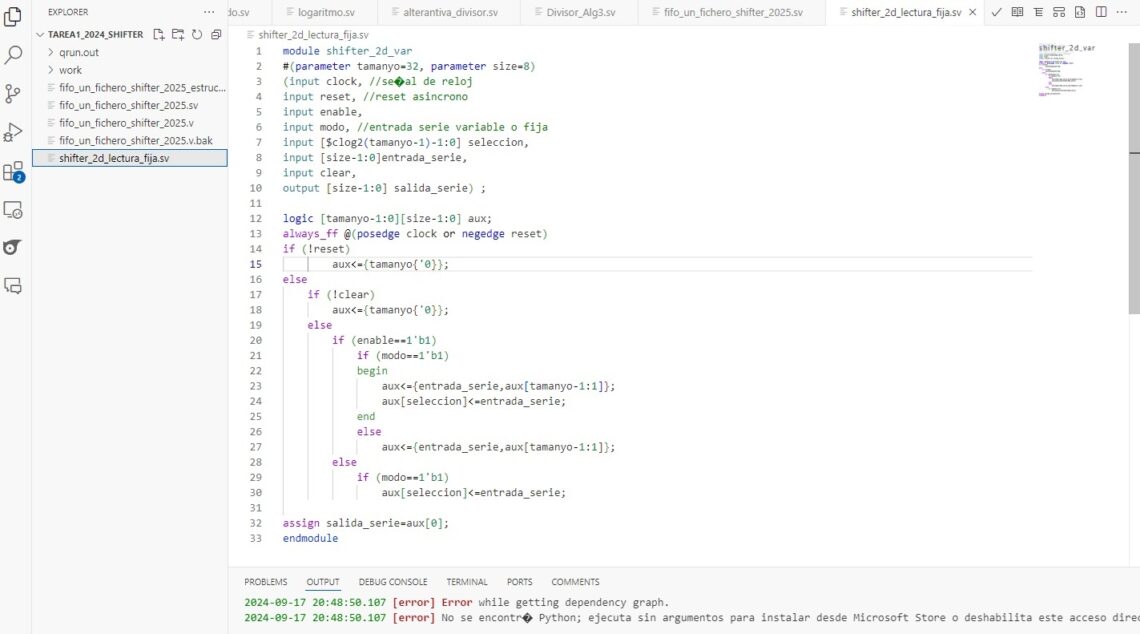

Vamos a ver con esta entrada cómo podemos diseñar y verificar hardware con un editor de amplio espectro como es Visual Studio Code. Control de versiones Sin duda alguna un editor potente que se precie debe de tener implementado un control de versiones que nos garantice dicho control a nivel local, tener copias de seguridad remotas con algún repositorio en…

-

-

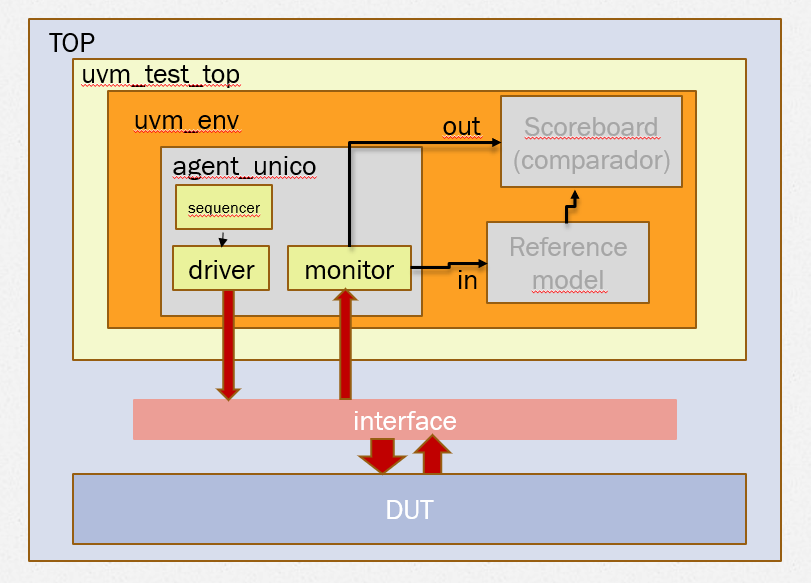

Sesion 3 Seminario Verificación UVM nivel básico

En esta sesión nos vamos a dedicarnos a la cobertura funcional y a mejorar nuestro plan de verificación con el fin de conseguir una grado de cobertura especificado. Para ello el esquema que vamos a seguir es el siguiente: Determinación de la cobertura funcional con el componente coverage Generación de nuevas secuencias y valoración del grado de cobertura obtenido Control…

-

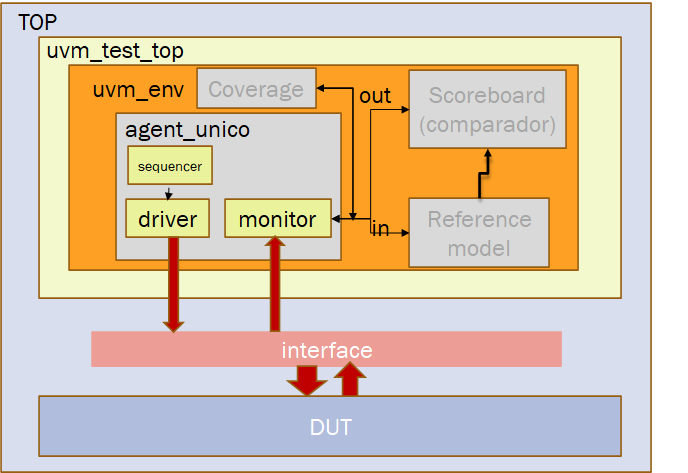

Sesion 2 Seminario Verificación UVM nivel básico

En esta sesión nos vamos a centrar en la creación del test de la siguiente figura (RECUADRO EN AMARILLO) y su posterior refinamiento, tanto de la generación de estímulos como en la observación de los resultados. El esquema que vamos a seguir es el siguiente: Creación del test Como puede observarse por los pasos a seguir es una metodología «bottom-up».…

-

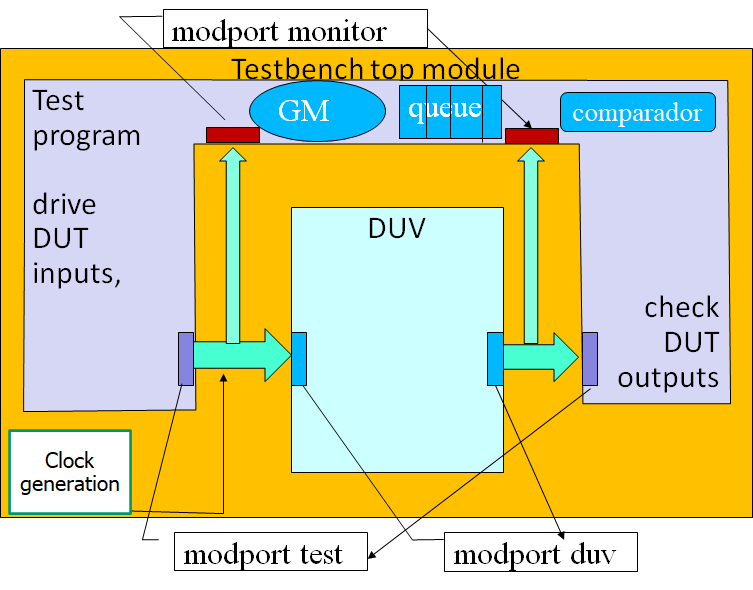

Sesion 1 Seminario Verificacion UVM nivel básico

Instrucciones iniciales Diseño a verificar Vamos a verificar un divisor algorítmico. El código ASM es el que se adjunta en la siguiente figura Os adjunto información de cómo deberían denominarse los puertos y de entrada y salida. Es muy importante respetar este tipo de nombres sobre todo si se quiere reusar un banco de pruebas previo. TerosHDL Entity: Divisor_Alg2 File:…