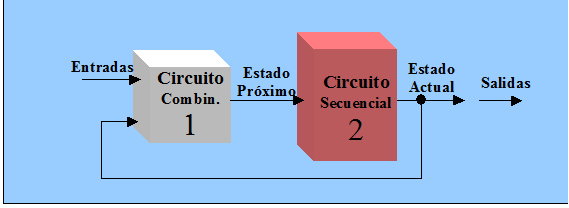

Uno de los casos más usuales en los cuales es necesario hacer una codificación especifica es aquel en el que las salidas están codificados en los estados, con lo cual eliminamos el circuito combinacional3, y por tanto tenemos las salidas libres de “glitches» y con el menor retardo posible. Estas máquinas son conocidas como máquinas Medvedev (ver Ilustración 5)

Ilustración 5. Modelo Medvedev

Evidentemente es una variante del modelo MOORE con la particularidad de tener una codificación en la cual algunas de las variables (bits) de estado asumen el valor de las salidas en cada uno de los estados. El precio de esta codificación especial es la necesidad, en la mayoría de los casos, de un mayor número de bits (flip-flops) que en una codificación de los estados secuencial.

Veamos esto con el ejemplo del detector de secuencia. Vamos a utilizar el tipo de datos reg por cuanto es el único que explícitamente nos puede permitir expresar esta codificación de las salidas en los estados.

module medvedev (RELOJ, RESET_A, SALIDA, ENTRADA);

input RELOJ,ENTRADA,RESET_A;

output SALIDA;

parameter [2:0] Q1=4'H0, Q2=4'H4, Q3=4'H2,Q4=4'H1 ;

reg [2:0] ESTADO, ESTADO_PROX;

always @(ESTADO or ENTRADA) //combinacional1

case (ESTADO) //synopsys full_case

Q1 : if (!ENTRADA) ESTADO_PROX=Q2;else ESTADO_PROX=Q1;

Q2 : if (ENTRADA) ESTADO_PROX=Q3; else ESTADO_PROX=Q2;

Q3 : if (!ENTRADA) ESTADO_PROX=Q4; else ESTADO_PROX=Q1;

Q4 : if (!ENTRADA) ESTADO_PROX=Q2;else ESTADO_PROX=Q3; endcase

always @(posedge RELOJ or negedge RESET_A) //secuencial2

if (!RESET_A) ESTADO <= Q1;

else ESTADO <= ESTADO_PROX ;

assign SALIDA=ESTADO[0];

endmoduleEjemplo 3. Descripción Verilog del detector de secuencia Medvedev.

Como puede observarse en el Ejemplo 3 la salida esta codificada en el bit menos significativo de la señal de estado, con lo cual no es necesaria ninguna circuitería combinacional adicional.

4.2.1. Realizando una máquina Medvedev

A continuación en el siguiente vídeo verás cómo se describe una FSM Medvedev.