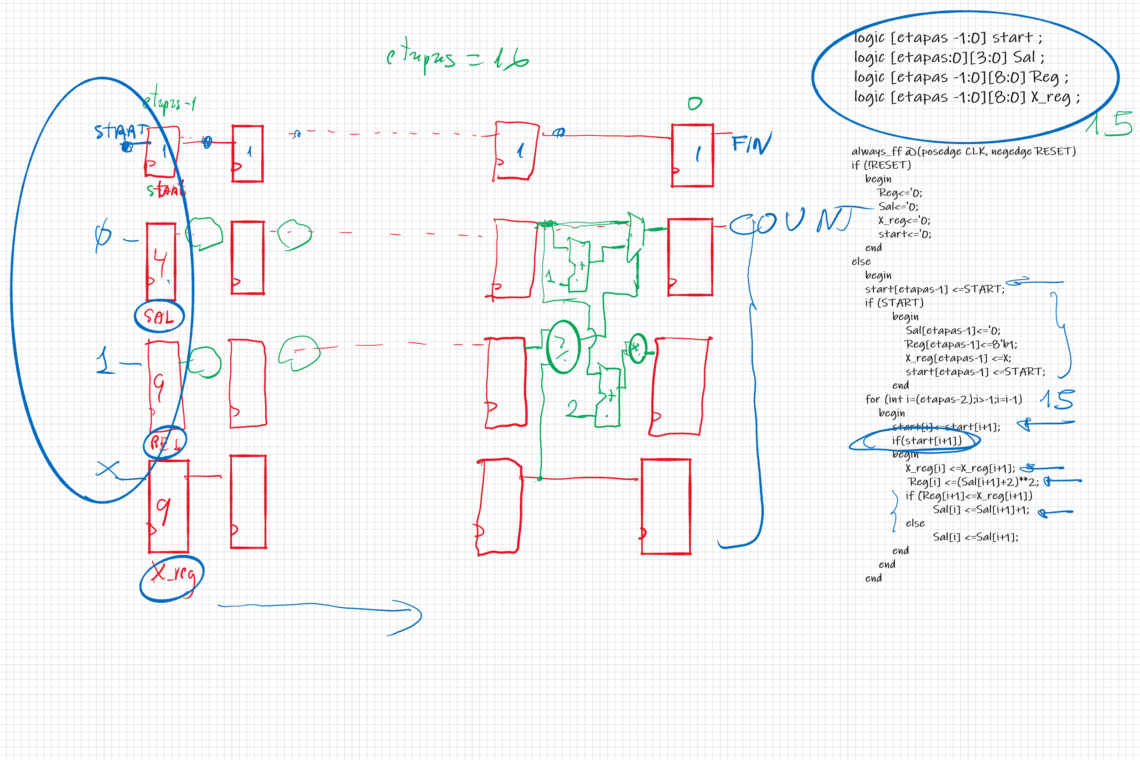

Paso 3: Realización de la segmentación Partimos por tanto de la siguiente descripción. Nuestra intención es ahora hacer la segmentación de esta descripción algorítmica escrita en SystemVerilog. El procedimineto de segmentación lo podemos observar en el siguiente vídeo Mostramos ahora el resultado de nuestra segmentación: Veamos ahora las prestaciones en área y velocidad conseguidas por esta segmentación realizada. De paso…

-

-

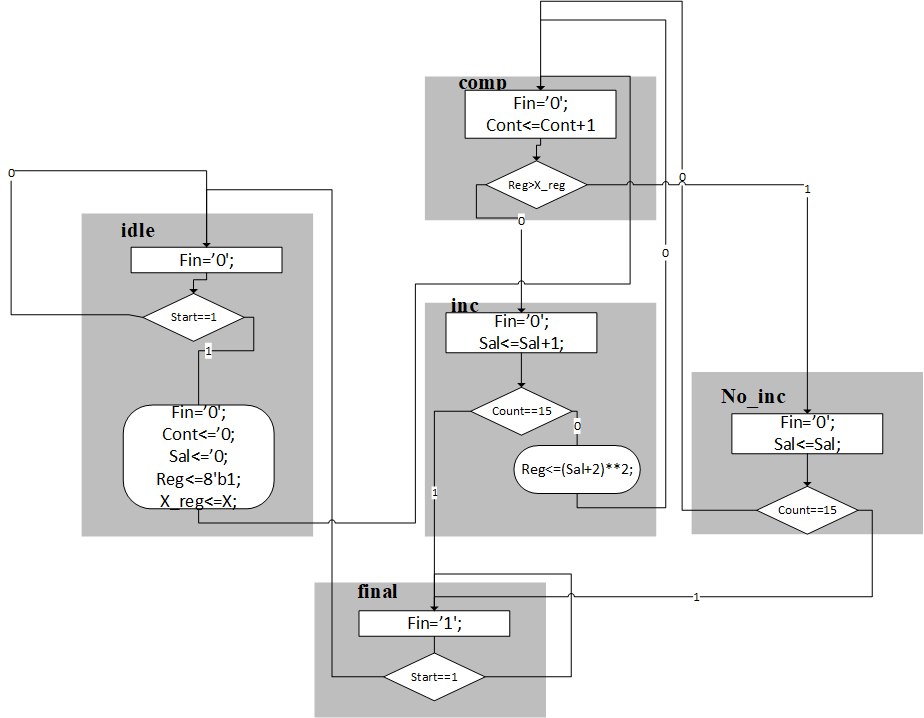

Realización de soluciones segmentadas II

Paso 2: Modificación de la latencia El resultado de este proceso de modificación del ASM, transcrito a SystemVerilog es el siguiente:

-

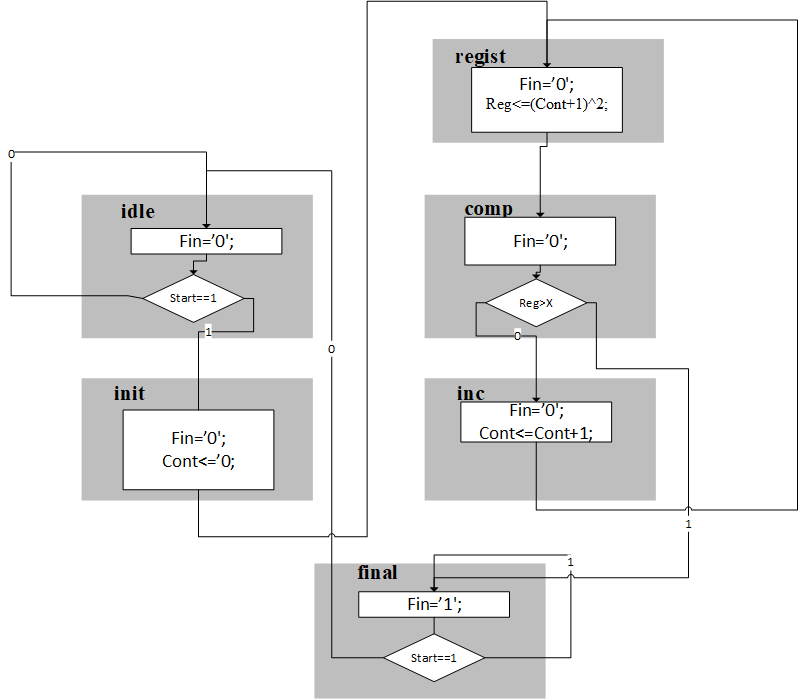

Realización de soluciones segmentadas I

Paso 1: Realización ASM con un solo fichero En esta entrada vamos a explicar cómo podemos describir directamente un ASM con un solo fichero. Este será nuestro primer paso para la consecución de una solución segmentada; pero nos va a servir para que podáis observar que el particionado Control-Path y Data-path puede ser acometido de forma diferente a como lo…

-

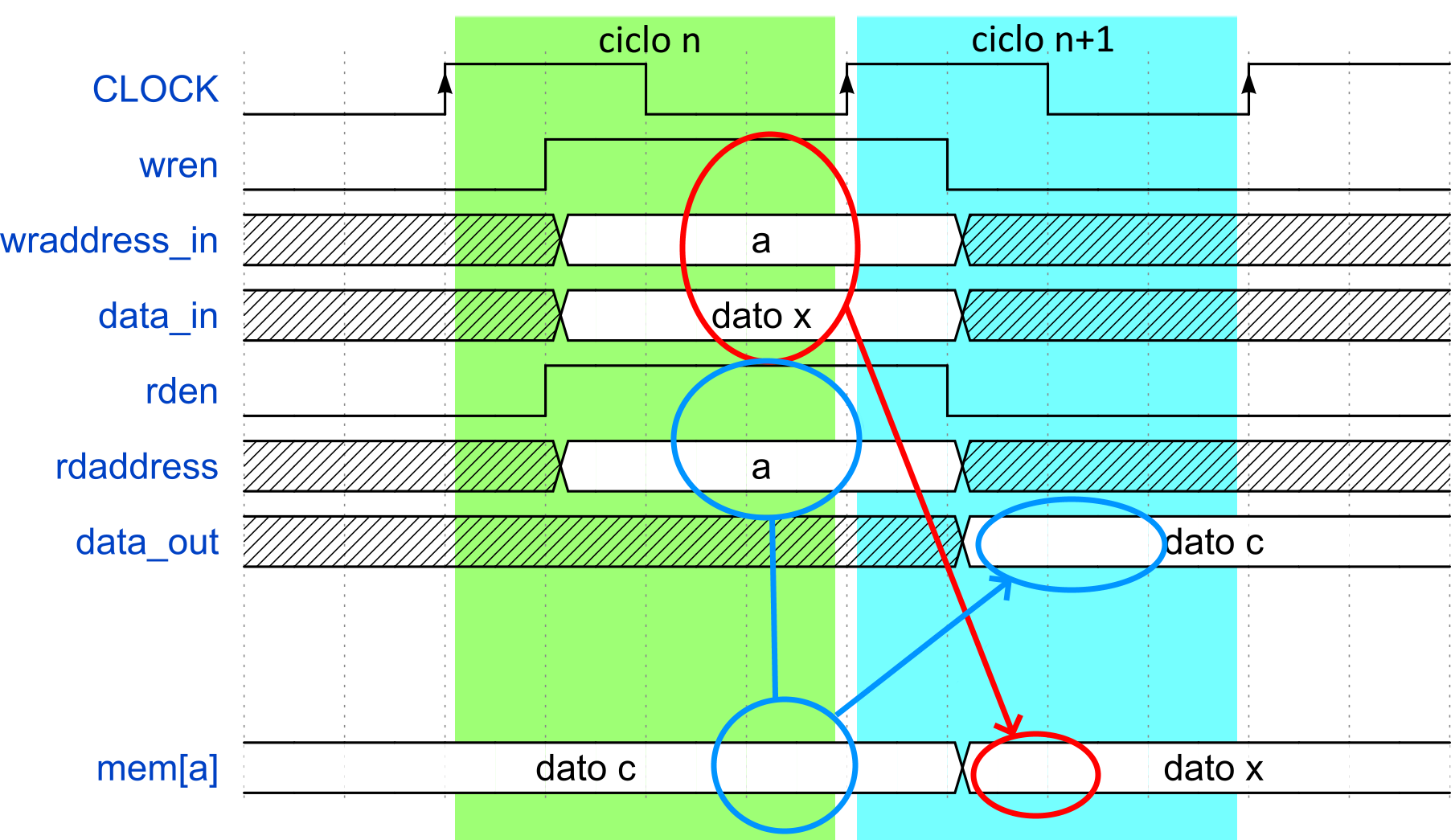

Lectura de la FIFO y su temporización. Problemas asociados.

La lectura de datos de la FIFO presenta confusiones debido a su temporización. Para ello hay que tener claro cuando ocurren las cosas. Cuando se solicita la lectura de datos y cuando esta lectura se hace efectiva. Lectura de la FIFO. La FIFO es un elemento secuencial, por tanto, los instantes importantes en los elementos secuenciales vienen determinados por el…

-

Verificación hardware de un microprocesador simple

Con este ejemplo queremos mostrar algunas características que puedan ser útiles en el diseño de sistemas más complejos; pero la arquitectura de este microprocesador (Multi-Cycle Processor) tiene poco que ver con las solicitadas en la tarea 3 fase 2 (single cycle processor) y 3 (pipeline processor) : Realización de un interfaz para modelar un bus triestado de interconexión de los…