En esta opción voy a comentar fundamentalmente dos nuevas incorporaciones que creo son las más destacables de esta evolución:

- El uso de clocking blocks para sincronización de los trasvases de información entre el program (testbench) y el diseño (DUV)

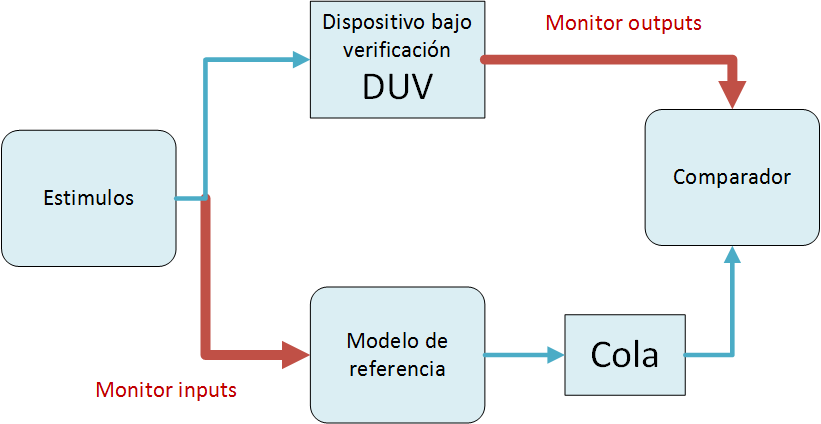

- El uso de tasks de monitorización para hacer llegar los estímulos del testbench al modelo de referencia y para comparar las respuestas del DUV con las obtenidas con el modelo de referencia

Cloking Block

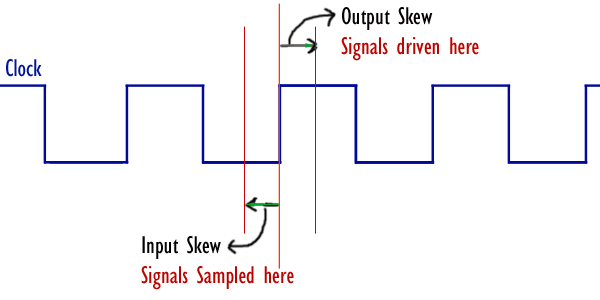

La idea es sincronizar en base al evento descrito en el clocking block, tal como muestra la siguiente figura:

Para entender mejor el comportamiento de los clocking blocks utilizados vamos a realizar la siguiente suposición. Supongamos que la señal de START tiene un skew (output skew) en el clocking block de generación de estímulos (sd) de 98 ns y un skew (input skew) de 5 ns en el clocking block de monitorización (md).

clocking sd @(posedge CLK);

default input #1ns output #1ns;

input COUNT,FIN ;

output #98ns START;

output X;

endclocking:sd

//efinimos el clocking de monitorizacion

clocking md @(posedge CLK);

default input #5ns output #1ns;

input COUNT,FIN,START,X ;

endclocking:md

Vamos a representar en un cronograma el comportamiento del estímulo generado (prueba_radicador/estim1/sd/START que lo llamaremos empieza_sd), cómo es percibido por el DUV (prueba_radicador/DUV/START que lo llamaremos START), y cómo es monitorizado por el modelo de referencia (prueba_radicador/estim1/md/START que lo llamaremos empieza_md).

Si visualizáramos como es percibido este estímulo por el DUV, veríamos que existe un retardo que coincide con el «skew» definido para las salidas del clocking block (sd).

También podemos ver como ese mismo estímulo llega al modelo de referencia a través de otro clocking block (md) también con el mismo evento base (flancos positivos del reloj). En este caso el estímulo llega retrasado dos ciclos de reloj, puesto que en dicho flanco de reloj (con un skew de adelanto de 5 ns) es cuando START tiene el valor 1. Para ver con detalle estas circunstancias, situarse con el ratón encima de la forma de onda, picar sobre la misma y modificar su zoom mediante la acción conjunta de la tecla control y la rueda del ratón

Monitorización

La monitorización de las entradas y de las salidas del DUV ha sido realizado mediante dos tasks con una estructura de un «loop» tipo «while»:

- Uno está monitorizando en todo momento cualquier cambio de las entradas (monitor_input) para llevar inmediatamente esos estímulos al modelo de referencia y el resultado de aplicar estos estímulos a dicho modelo (respuesta esperada) guardarlo en una FIFO

- El otro está monitorizando en todo momento las salidas (monitor_output) del DUV para llevar inmediatamente dichas salidas a una aserción que compara este comportamiento de las salidas con las esperadas que tengo almacenadas en la FIFO (tras la extracción de las mismas)

Laboratorio virtual

https://www.edaplayground.com/x/4Hx_