RAM de lectura asíncrona

- Así se las denomina a las que cambian el puerto de salida cuando cambia la dirección de lectura sin la necesidad de ningún flanco de reloj adicional

- No suele ser posible en la mayoría de las memorias embebidas de la mayoría de los fabricantes (XILINX, IntelFPGA, etc)

- Sin embargo es posible en las memoras distribuidas de XILINX que implementan esta memoria con las CLB o slices y no utilizan los bloques embebidos de memoria

- También es posible en las nuevas familias Cyclone 10, ARRIA 10 y STRATIX 10 de INtelFPGA mediante los MLAB

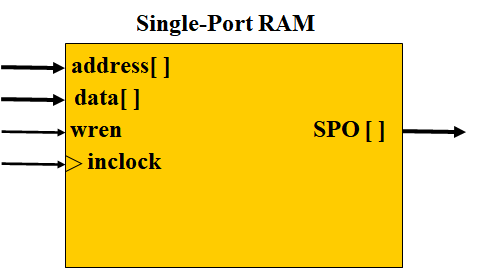

RAM “single port”

Entendidas como aquellas memorias que solo disponen de una entrada de direcciones (un solo posible acceso en cada instante) que sirve indistintamente a la escritura como a la lectura

Ejemplo. Modelo de la memoria asíncrona “single port”

module ram_synch_in (data_in,

address, wren, inclock,

SPO);

parameter d_width = 16;

parameter a_width = 6;

input [d_width-1:0] data;

input [a_width-1:0] address;

input wren, inclock;

output [d_width-1:0] SPO;

logic [d_width-1:0] mem[(1<<a_width)-1:0];

always_ff @(posedge inclock)

if (wr_en)

mem[address] <=data_in;

assign SPO = mem[address];

endmodule

module ram_synch_in (data_in,

address, wren, inclock,

SPO);

parameter d_width = 16;

parameter a_width = 6;

input [d_width-1:0] data;

input [a_width-1:0] address;

input wren, inclock;

output [d_width-1:0] SPO;

logic [d_width-1:0] mem[(1<<a_width)-1:0];

always_ff @(posedge inclock)

if (wr_en)

mem[address] <=data_in;

assign SPO = mem[address];

endmodule

RAM síncrona

- Cambian el puerto de salida cuando cambia la dirección de lectura con la necesidad de un flanco de reloj adicional

- Las memorias embebidas de la mayoría de los fabricantes son de este tipo (XILINX, IntelFPGA, etc)

- La tendencia es que estas memorias sean “True Dual port” y que permitan trabajar con relojes independientes en cada uno de los puertos

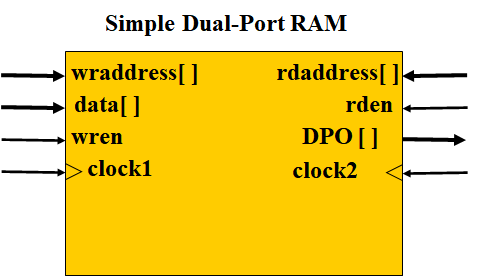

RAM «DUAL port»

- Disponen de dos entrada de direcciones (dos accesos simultáneos) si bien en su versión “simple” necesariamente una dirección servirá para una acceso de lectura y la otra dirección para un acceso de escritura.

- Si estos accesos pueden ser configurados como lectura o escritura independientemente de cómo trabaje el otro acceso estaremos hablando de “True Dual Port”

RAM síncrona «Simple Dual Port»

Existen dos estilos:

- Registrar el puerto de salida

- Históricamente era más natural para XILINX que para IntelFPGA cuando se utiliza un sintetizador generalista: Leonardo, Synplify. Lo cual obliga a utilizar muchas veces pragmas para ayudar a la inferencia sobre IntelFPGA.

- Con el sintetizador de Quartus no hace falta pragmas y no infiere automáticamente ”glue logic” para evitar desavenencias pre-post síntesis en el caso de lectura y escritura simultánea sobre la misma dirección, de lo cual eres advertido.

- Da una idea de que si utilizamos el mismo reloj para ambos puertos y escribimos y leemos de la misma dirección, el dato extraído por el puerto de salida sería el antiguo.

module ram_dp #(parameter mem_depth=32, parameter size=8)

(

input [size-1:0] data,

input wren,clock1,clock2,rden,

input [$clog2(mem_depth-1)-1:0] wraddress,

input [$clog2(mem_depth-1)-1:0] rdaddress,

output logic [size-1:0] DPO

);

logic [size-1:0] mem [mem_depth-1 :0];

always_ff @(posedge clock1)

if (wren==1'b1)

mem[wraddress]<=data_in;

always_ff @(posedge clock2)

if (rden==1'b1)

DPO<=mem[rdaddress];

endmodule

- Registrar la dirección de lectura

- Históricamente era más natural para IntelFPGA cuando se utiliza un sintetizador generalista: Leonardo, Synplify.

- En el caso del sintetizador de Quartus . Si añade lógica adicional para evitar desavenencias para el caso simultáneo de lectura y escritura sobre la misma dirección

- Da una idea de que si utilizamos el mismo reloj para ambos puertos y escribimos y leemos de la misma dirección, el dato extraído por el puerto de salida sería el nuevo.

module ram_dp #(parameter mem_depth=32, parameter size=8)

(

input [size-1:0] data,

input wren,clock1,clock2,rden,

input [$clog2(mem_depth-1)-1:0] wraddress,

input [$clog2(mem_depth-1)-1:0] rdaddress,

output logic [size-1:0] DPO

);

logic [size-1:0] mem [mem_depth-1 :0];

logic [$clog2(mem_depth-1)-1:0] rdaddress_reg,

always_ff @(posedge clock1)

if (wren==1'b1)

mem[wraddress]<=data_in;

always_ff @(posedge clock2)

if (rden==1'b1)

rdaddress_reg<=rdaddress;

assign DPO<=mem[rdaddress_reg];

endmodule

Inferencia de memorias RAM

Todos los códigos expuestos intentan que tu SystemVerilog infiera automáticamente la RAM de las características deseadas. Sin embargo hay que reconocer que a veces hay que leerse la letra pequeña del sintetizador que tienes entre manos para conseguir exactamente lo que deseas y muy posiblemente tengas que recurrir a pragmas y atributos específicos de la herramienta

Por ejemplo es posible que desees que el sintetizador utilice una alternativa específica de implementación (si memorias embebidas o utilización de logic cells) y que no introduzca lógica adicional para evitar desavenencias pre-post síntesis. En Quartus deberíamos emplear el siguiente atributo que se colocaría antes de la declaración del array bidimensional:

- (* ramstyle = «MLAB, no_rw_check» *) logic [d_width-1:0] mem[1<<a_width:0]/ ;