Instrucciones iniciales Diseño a verificar Vamos a verificar una FIFO síncrona. El código ASM es el que se adjunta en la siguiente figura Os adjunto información de cómo deberían denominarse los puertos y de entrada y salida. Es muy importante respetar este tipo de nombres sobre todo si se quiere reusar un banco de pruebas previo. Comportamiento El comportamiento es…

-

-

Clases

-

Verificación Formal (I)

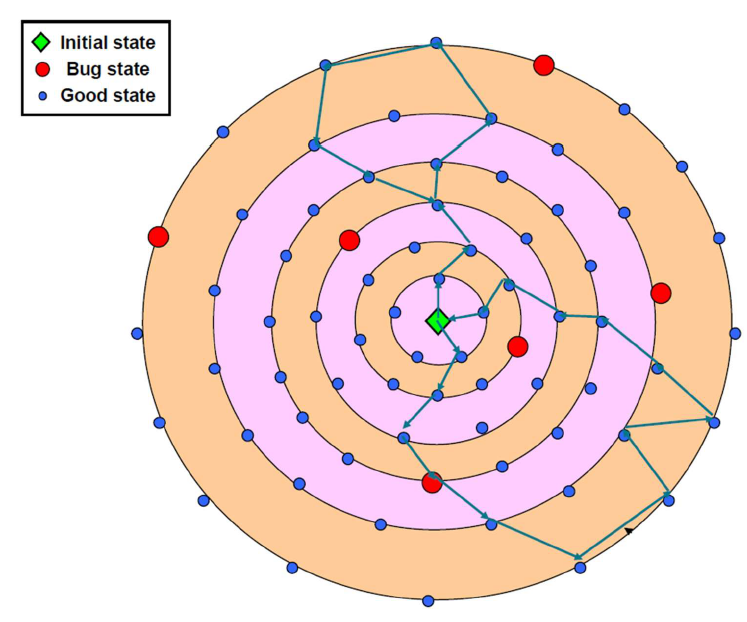

¿Qué es verificación formal? La verificación formal (FV) consiste en el uso de herramientas que analizan matemáticamente el espacio de comportamientos posibles de un diseño, en lugar de calcular resultaos para valores particulares. Es decir, una herramienta de FV examina el conjunto completo de posibles simulaciones utilizando técnicas matemáticas, en contraste con la simulación, que evalúa puntos individuales en ese…

-

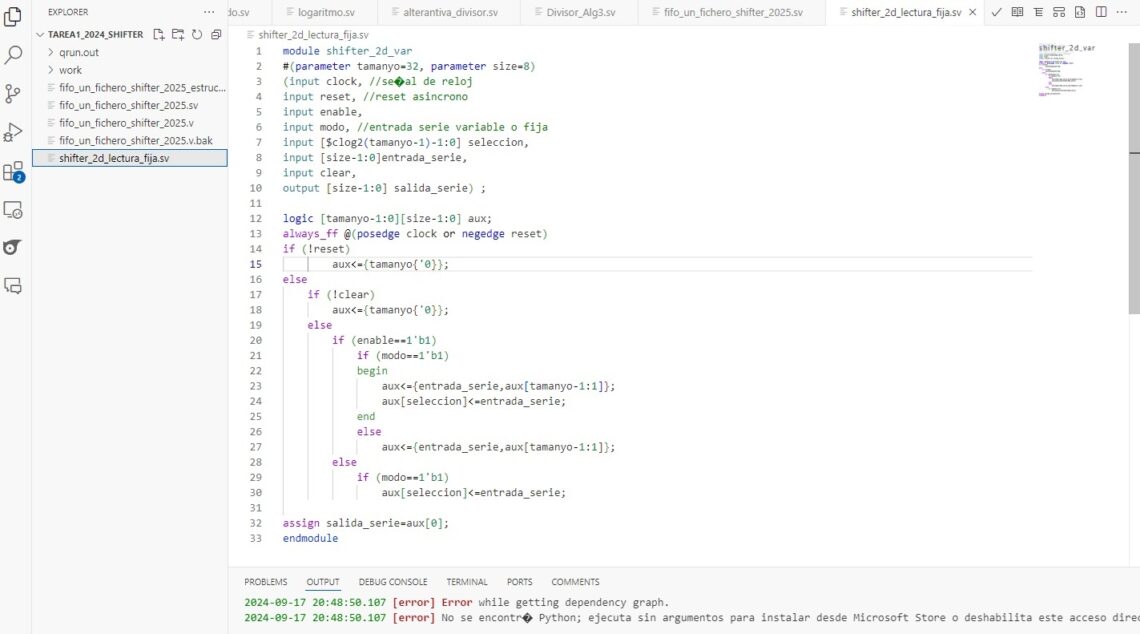

Trabajo con un editor como centro de operaciones de diseño y verificación: Parte I

Vamos a ver con esta entrada cómo podemos diseñar y verificar hardware con un editor de amplio espectro como es Visual Studio Code. Control de versiones Sin duda alguna un editor potente que se precie debe de tener implementado un control de versiones que nos garantice dicho control a nivel local, tener copias de seguridad remotas con algún repositorio en…

-

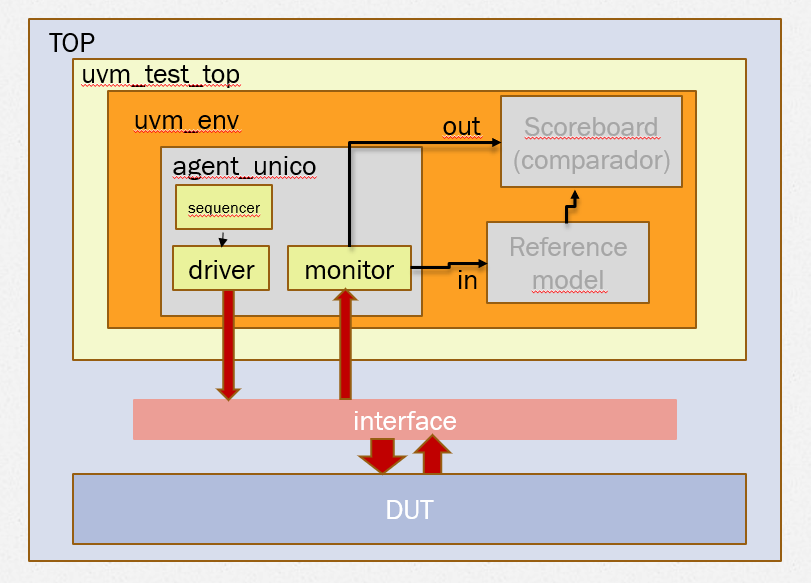

Sesion 3 Seminario Verificación UVM nivel básico

En esta sesión nos vamos a dedicarnos a la cobertura funcional y a mejorar nuestro plan de verificación con el fin de conseguir una grado de cobertura especificado. Para ello el esquema que vamos a seguir es el siguiente: Determinación de la cobertura funcional con el componente coverage Generación de nuevas secuencias y valoración del grado de cobertura obtenido Control…

-

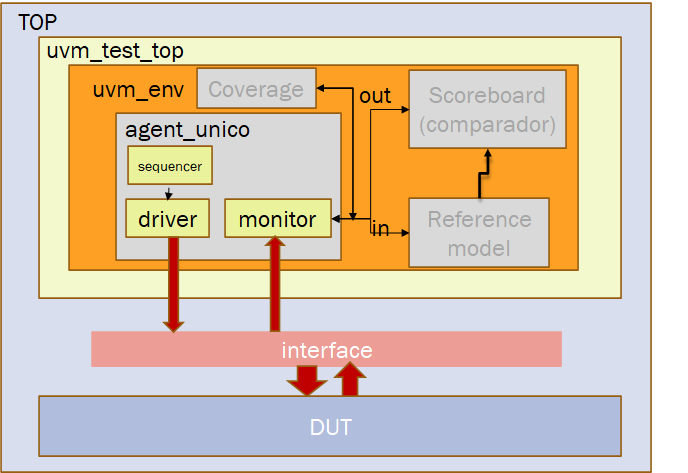

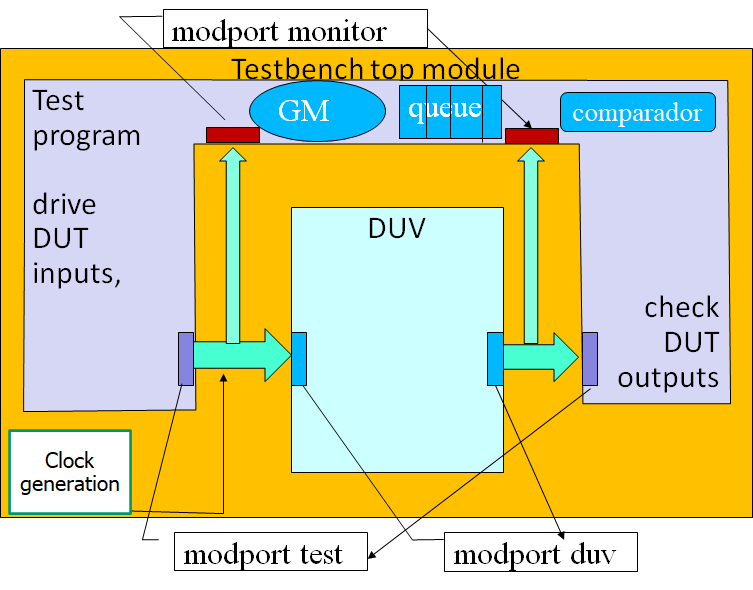

Sesion 2 Seminario Verificación UVM nivel básico

En esta sesión nos vamos a centrar en la creación del test de la siguiente figura (RECUADRO EN AMARILLO) y su posterior refinamiento, tanto de la generación de estímulos como en la observación de los resultados. El esquema que vamos a seguir es el siguiente: Creación del test Como puede observarse por los pasos a seguir es una metodología «bottom-up».…

-

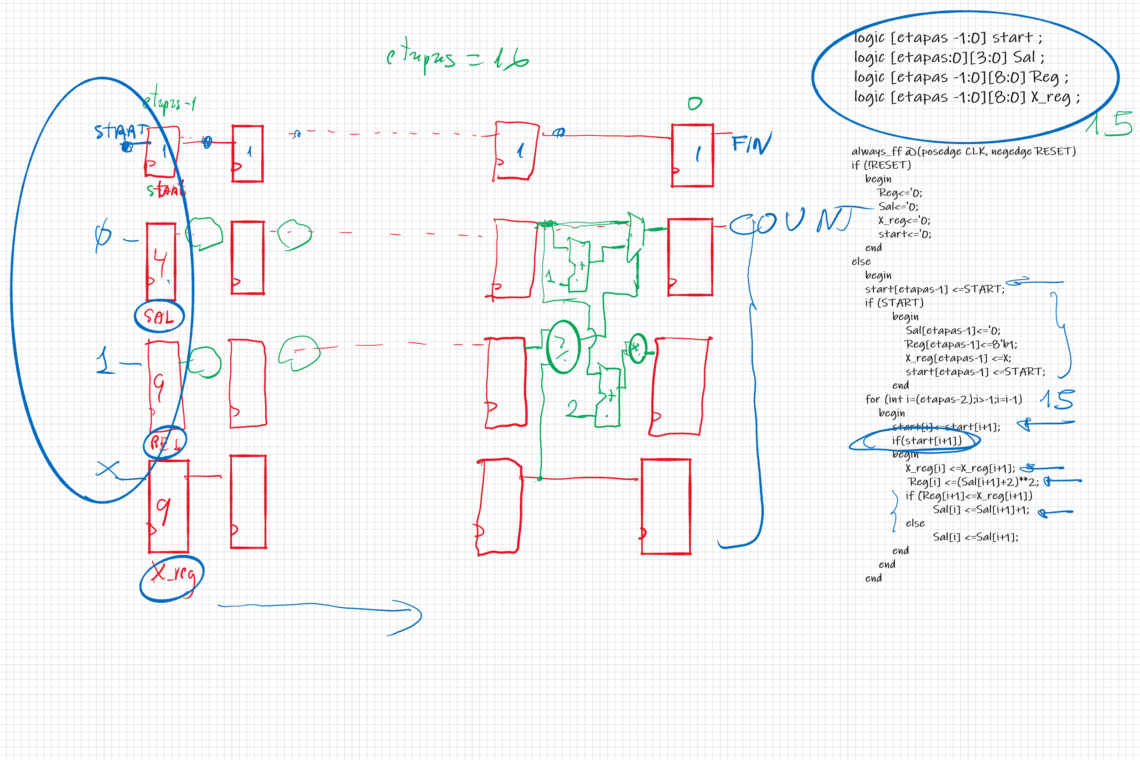

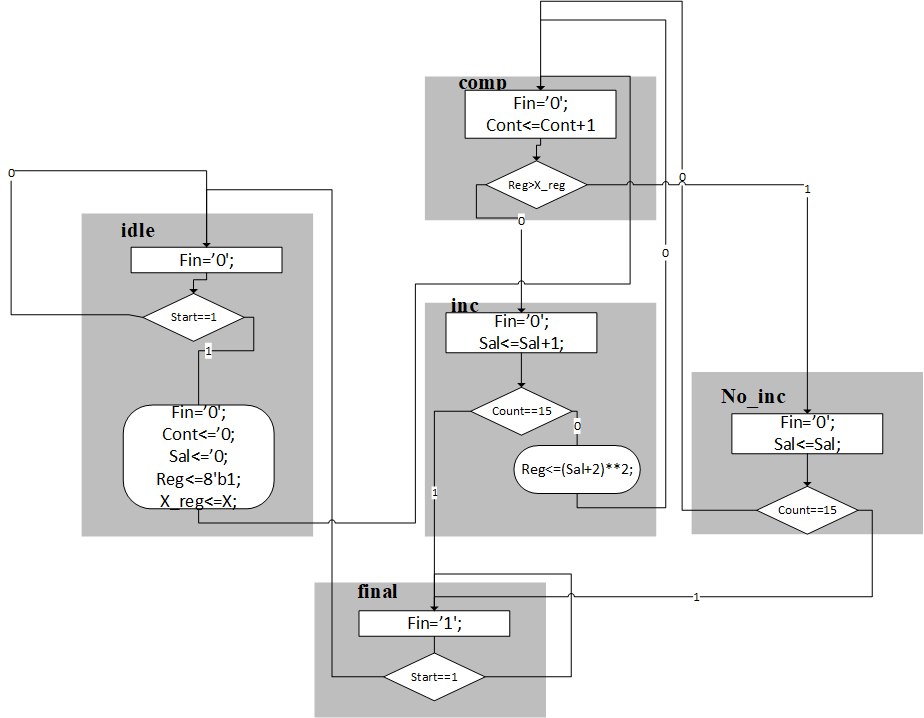

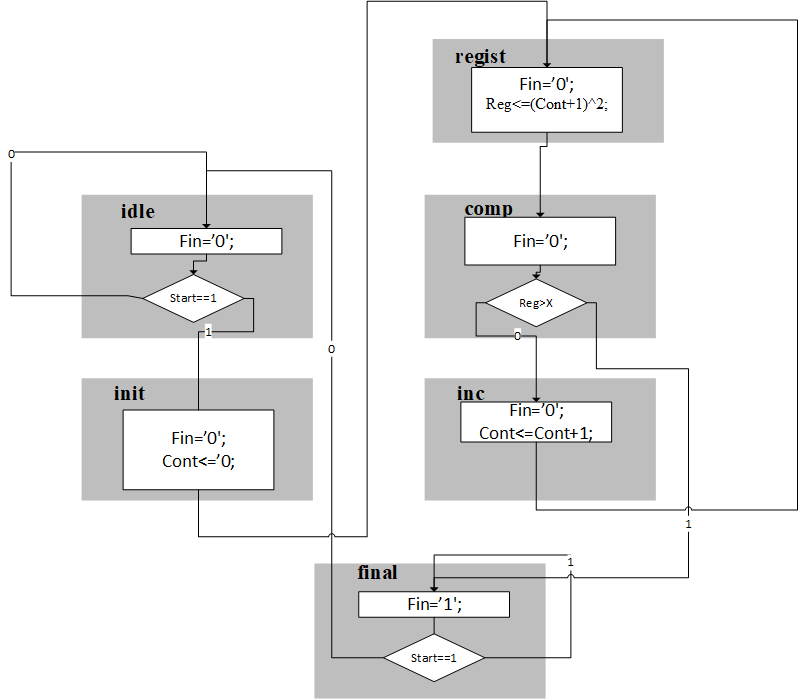

Sesion 1 Seminario Verificacion UVM nivel básico

Instrucciones iniciales Diseño a verificar Vamos a verificar un divisor algorítmico. El código ASM es el que se adjunta en la siguiente figura Os adjunto información de cómo deberían denominarse los puertos y de entrada y salida. Es muy importante respetar este tipo de nombres sobre todo si se quiere reusar un banco de pruebas previo. TerosHDL Entity: Divisor_Alg2 File:…

-

Realización de soluciones segmentadas III

Paso 3: Realización de la segmentación Partimos por tanto de la siguiente descripción. Nuestra intención es ahora hacer la segmentación de esta descripción algorítmica escrita en SystemVerilog. El procedimineto de segmentación lo podemos observar en el siguiente vídeo Mostramos ahora el resultado de nuestra segmentación: Veamos ahora las prestaciones en área y velocidad conseguidas por esta segmentación realizada. De paso…

-

Realización de soluciones segmentadas II

Paso 2: Modificación de la latencia El resultado de este proceso de modificación del ASM, transcrito a SystemVerilog es el siguiente:

-

Realización de soluciones segmentadas I

Paso 1: Realización ASM con un solo fichero En esta entrada vamos a explicar cómo podemos describir directamente un ASM con un solo fichero. Este será nuestro primer paso para la consecución de una solución segmentada; pero nos va a servir para que podáis observar que el particionado Control-Path y Data-path puede ser acometido de forma diferente a como lo…