Modelo de bloques

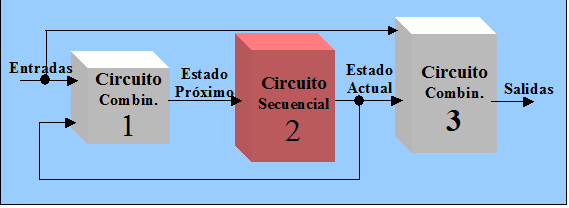

La funcionalidad del modelo Mealy podemos verla representada en la Ilustración 4, destacando, a diferencia del modelo Moore, que el circuito combinacional de salida depende tanto del estado como de las entradas.

Ilustración 4. Modelo Mealy

Modelo Verilog

Como puede adivinarse, los procesos combinacional1 y secuencial2 son totalmente equivalentes al modelo Moore y tan solo el proceso combinacional3 debe reflejar su dependencia en la lista de sensibilidad a los cambios que puedan producirse en las entradas que lógicamente son leídas en el interior de la descripción. Así de esta forma tendríamos lo siguiente:

combinacional1: always @( entradas or estado_actual)

proceso sensible a las entradas y al estado de la máquina. En este proceso, de tipo combinacional, modelizaremos el circuito combinacional que nos obtiene el próximo estado de la máquina Mealy.

secuencial2: always @(posedge reloj or negedge reset_a)

proceso que modelizará la lógica secuencial. Se encargará de que en el flanco activo del reloj el estado de la máquina pase a ser el valor que en ese momento tenga el próximo estado. También en este proceso se modelizará la acción del reset de la máquina, sea asíncrono o síncrono.

combinacional3: always @(estado_actual, entradas)

proceso sensible al estado de la máquina y a las entradas. En este proceso, de tipo combinacional, modelizaremos el circuito combinacional de las salidas.

Como hemos dicho anteriormente, una variante muy habitual es combinar los dos procesos combinacionales en uno solo, puesto que ambos comparten la misma lista de sensibilidad y en ambos es necesario recorrer de igual forma las diferentes transiciones que ocurren desde cada estado y ante cualquier combinación de entradas, para determinar cual es el estado siguiente y la salida asociada a dicha transición. En el ejemplo seguiremos aplicando la variante de los tres procesos.

Ejemplo

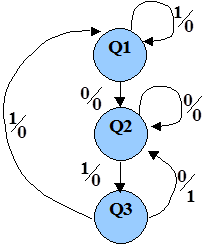

El diagrama de estado correspondiente al detector de secuencias bajo un modelo Mealy es el representado en la Ilustración 5 y su correspondiente descripción Verilog la tenemos en Ejemplo 2.

Ilustración 5. Diagrama de estados Mealy

module FSM_10 (

input RELOJ,

input RESET_A,

output logic SALIDA,

input ENTRADA);

parameter [2:0] Q1=3'h0, Q2=3'h3, Q3=3'h5 ;

logic [2:0] ESTADO, ESTADO_PROX;

always_ff @(posedge RELOJ or negedge RESET_A)

if (!RESET_A) ESTADO <= Q1;

else ESTADO <= ESTADO_PROX ;

always_comb

unique case (ESTADO)

Q1 : if (!ENTRADA) ESTADO_PROX=Q2;

Q2 : if (ENTRADA) ESTADO_PROX=Q3;

Q3 : if (!ENTRADA) ESTADO_PROX=Q2;

else ESTADO_PROX=Q1;

endcase

always_comb

case (ESTADO)

Q1 : SALIDA=1'b0;

Q2 : SALIDA=1'b0;

Q3 : if (!ENTRADA) SALIDA=1'b1;

else SALIDA=1'b0;

default: SALIDA=1'bx;

endcase

endmodule

module FSM_10 (

input RELOJ,

input RESET_A,

output logic SALIDA,

input ENTRADA);

parameter [2:0] Q1=3'h0, Q2=3'h3, Q3=3'h5 ;

logic [2:0] ESTADO, ESTADO_PROX;

always_ff @(posedge RELOJ or negedge RESET_A)

if (!RESET_A) ESTADO <= Q1;

else ESTADO <= ESTADO_PROX ;

always_comb

unique case (ESTADO)

Q1 : if (!ENTRADA) ESTADO_PROX=Q2;

Q2 : if (ENTRADA) ESTADO_PROX=Q3;

Q3 : if (!ENTRADA) ESTADO_PROX=Q2;

else ESTADO_PROX=Q1;

endcase

always_comb

case (ESTADO)

Q1 : SALIDA=1'b0;

Q2 : SALIDA=1'b0;

Q3 : if (!ENTRADA) SALIDA=1'b1;

else SALIDA=1'b0;

default: SALIDA=1'bx;

endcase

endmodule

Ejemplo 2. Descripción Verilog del detector de secuencia Mealy.

Realizando FSM Mealy con Verilog

1. Estilo de tres procesos

A continuación en el siguiente vídeo verás cómo se describe una FSM Mealy con un estilo de tres procesos.

2. Estilo de dos procesos

A continuación en el siguiente vídeo verás cómo se describe una FSM Mealy con un estilo de tres procesos.

Estados espúreos

En el ejemplo que acabamos de ver el sintetizador suele implementar dos flip-flops para almacenar el estado de la máquina, sin embargo la máquina solo dispone de tres estados normales, luego existirá una combinación de la variables de estados que constituirá un estado espúreo. ¿Qué hace el sintetizador con los estados espúreos?.

Lo que se haga con ellos dependerá de la herramienta de síntesis que se utilice; afortunadamente la mayoría de ellas tienen como opción de síntesis el utilizar un criterio de coste mínimo: el circuito será lo más rápido y pequeño posible a costa de no importarle lo que le ocurra a la máquina cuando entra en un estado espúreo; o un criterio de riesgo mínimo: el circuito no será tan óptimo en área y velocidad pero estará protegido ante la aparición de estados espúreos, es decir, lo hará transitar rápidamente a un estado normal de funcionamiento.

Sin embargo mi recomendación personal ante este tipo de situaciones sería que no confiáramos en esas magnificas opciones del sintetizador (en la mayoría suelen aparecer) y que explícitamente en nuestro código procuráramos la solución con riesgo mínimo. ¿Cómo?. Pues sencillamente con la opción de default del case llevando el estado espúreo a un estado normal de funcionamiento.