En esta opción vamos a realizar fundamentalmente dos grandes incorporaciones:

- La inclusión de todo el banco de pruebas bajo la construcción program

- la inclusión de un modelo de referencia

Construcción program

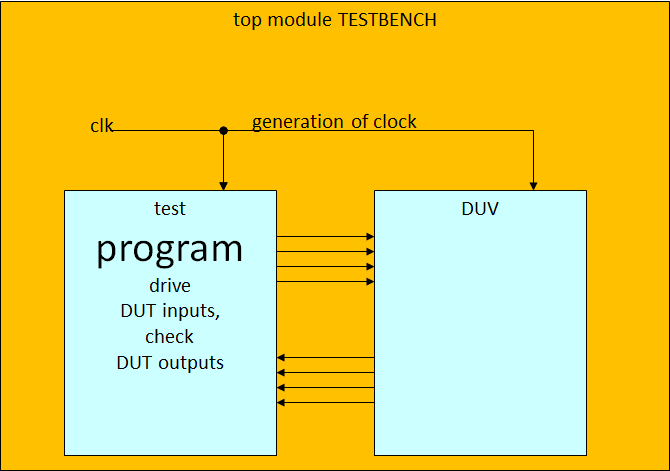

En cuanto a la primera incorporación, vemos que casi todo lo que habíamos definido bajo el module de jerarquía superior (denominado prueba radicador) especificando información del testbench (generación de estímulos y observación de resultados) lo hemos encapsulado bajo una construcción que específicamente se creó en Systemverilog para tal menester (en Verilog se solía encapsular en otro module). Con ello nos acercamos a lo que gráficamente expresa la siguiente figura:

Modelo de referencia

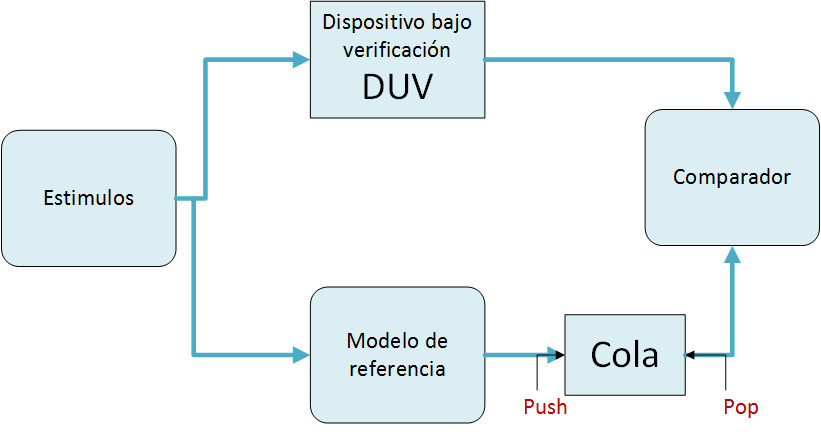

Vamos a introducir un modelo de referencia, con la intención de que cada vez que metamos nuevos estímulos a nuestro DUV , sean llevados igualmente a nuestro modelo de referencia (push), de forma que cuando observemos los resultados de nuestro DUV, podamos compararlos con los obtenidos idealmente en nuestro modelo de referencia (pop). Ahora la colocación de dicho modelo y cómo hago llevar los estímulos al modelo y cómo comparo lo que da la DUV y el modelo serán muy básicos; sin embargo es muy destacable el papel ejercido por una cola que sirve para adaptar el comportamiento temporal de nuestra DUV (en este caso multiciclo) con el comportamiento temporal de nuestro modelo ideal, tal como se observa en la siguiente figura:

Laboratorio virtual

https://www.edaplayground.com/x/3NHF