Instrucciones iniciales Diseño a verificar Vamos a verificar una FIFO síncrona. El código ASM es el que se adjunta en la siguiente figura Os adjunto información de cómo deberían denominarse los puertos y de entrada y salida. Es muy importante respetar este tipo de nombres sobre todo si se quiere reusar un banco de pruebas previo. Comportamiento El comportamiento es…

-

-

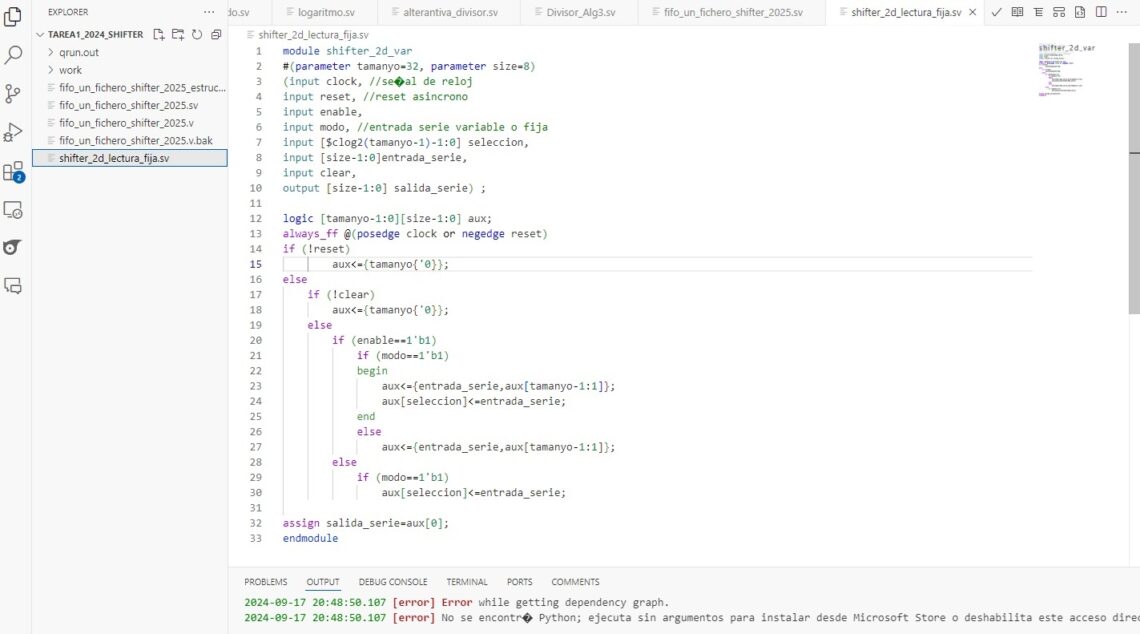

Trabajo con un editor como centro de operaciones de diseño y verificación: Parte I

Vamos a ver con esta entrada cómo podemos diseñar y verificar hardware con un editor de amplio espectro como es Visual Studio Code. Control de versiones Sin duda alguna un editor potente que se precie debe de tener implementado un control de versiones que nos garantice dicho control a nivel local, tener copias de seguridad remotas con algún repositorio en…

-

Grupo Pars

-

Simulación básica con colas