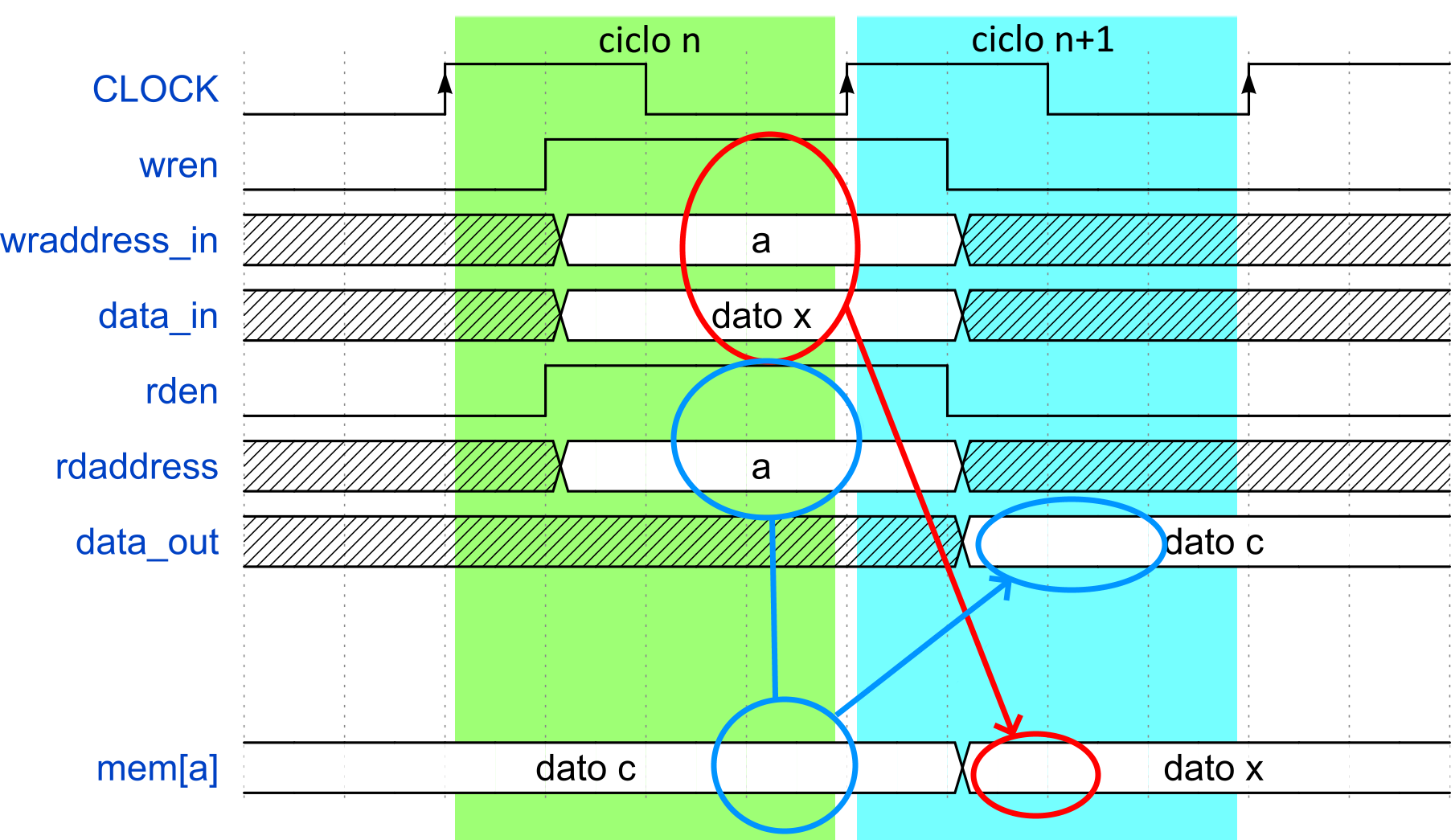

La lectura de datos de la FIFO presenta confusiones debido a su temporización. Para ello hay que tener claro cuando ocurren las cosas. Cuando se solicita la lectura de datos y cuando esta lectura se hace efectiva. Lectura de la FIFO. La FIFO es un elemento secuencial, por tanto, los instantes importantes en los elementos secuenciales vienen determinados por el…

-

-

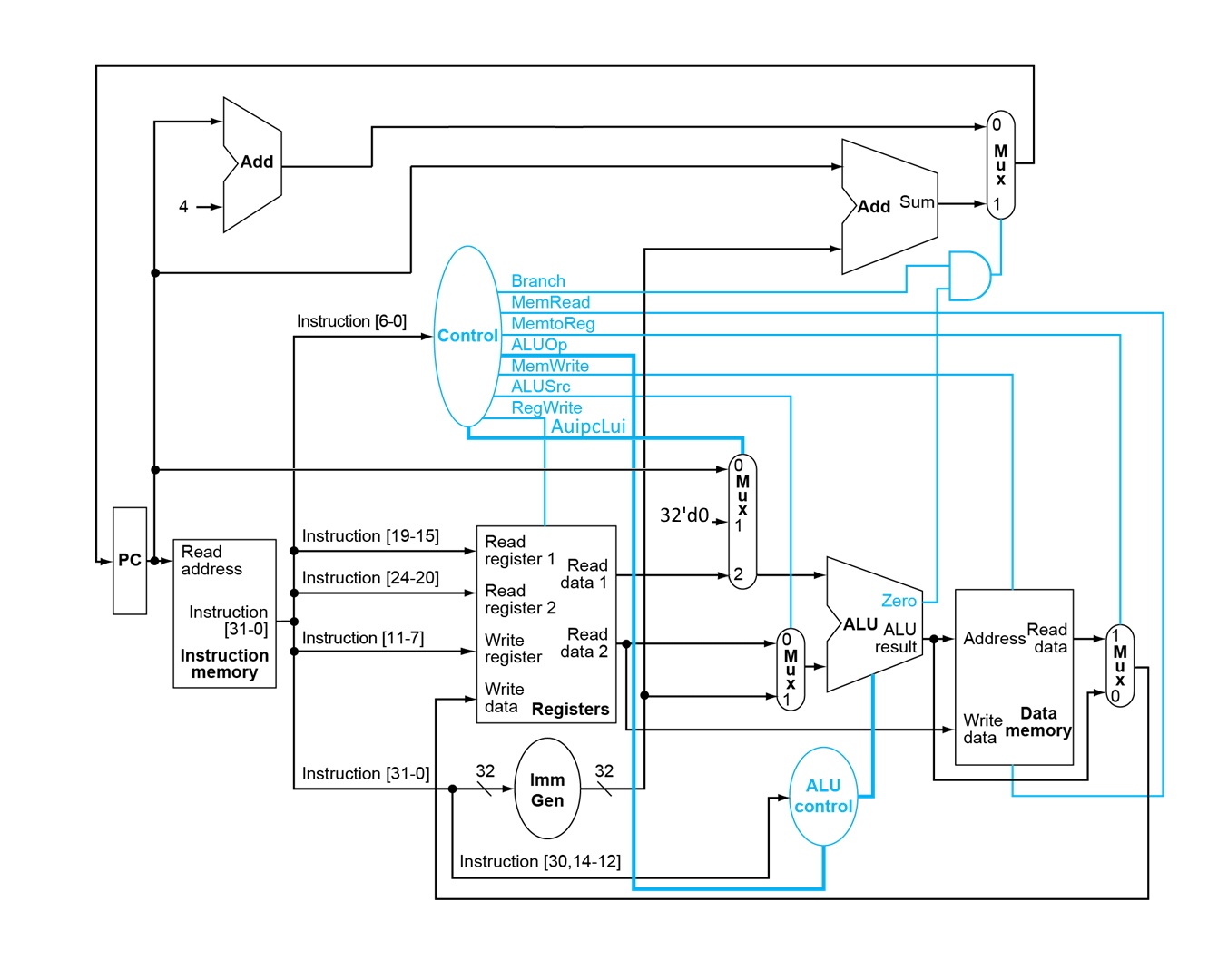

RISC-V: Instrucciones auipc y lui en la implementación monociclo.

Para hacer compatible los programas desarrollados en Venus en nuestra implementación monociclo del RISC-V, sería muy útil el uso en nuestro RISC-V de instrucciones para cargar direcciones de memoria en registros, como puede ser la (load address) o li (load immediate). Las instrucciones la y li son realmente pseudoinstrucciones. El compilador crea dos instrucciones para la (auipc + addi) y…