La lectura de datos de la FIFO presenta confusiones debido a su temporización.

Para ello hay que tener claro cuando ocurren las cosas. Cuando se solicita la lectura de datos y cuando esta lectura se hace efectiva.

Lectura de la FIFO.

La FIFO es un elemento secuencial, por tanto, los instantes importantes en los elementos secuenciales vienen determinados por el flanco de reloj.

En un diseño dado, la lógica, genera un resultado en las salidas ante un valor de las entradas. En el caso de la lógica secuencial las entradas son muestreadas (leídas) sólo en un instante dado, en el flanco de reloj.

Las ENTRADAS, por tanto, deben estar estables un tiempo ANTES del flanco de reloj (tiempo de setup) y un tiempo después (tiempo de hold) para que puedan ser capturadas de forma adecuada cuando este flanco de reloj llegue. Una vez las entradas son capturadas la lógica de generación de las salidas puede calcular un resultado. Por tanto, las SALIDAS se generan siempre DESPUÉS del flanco de reloj que capturó las entradas.

Teniendo esto claro vamos a analizar el proceso de lectura de la FIFO:

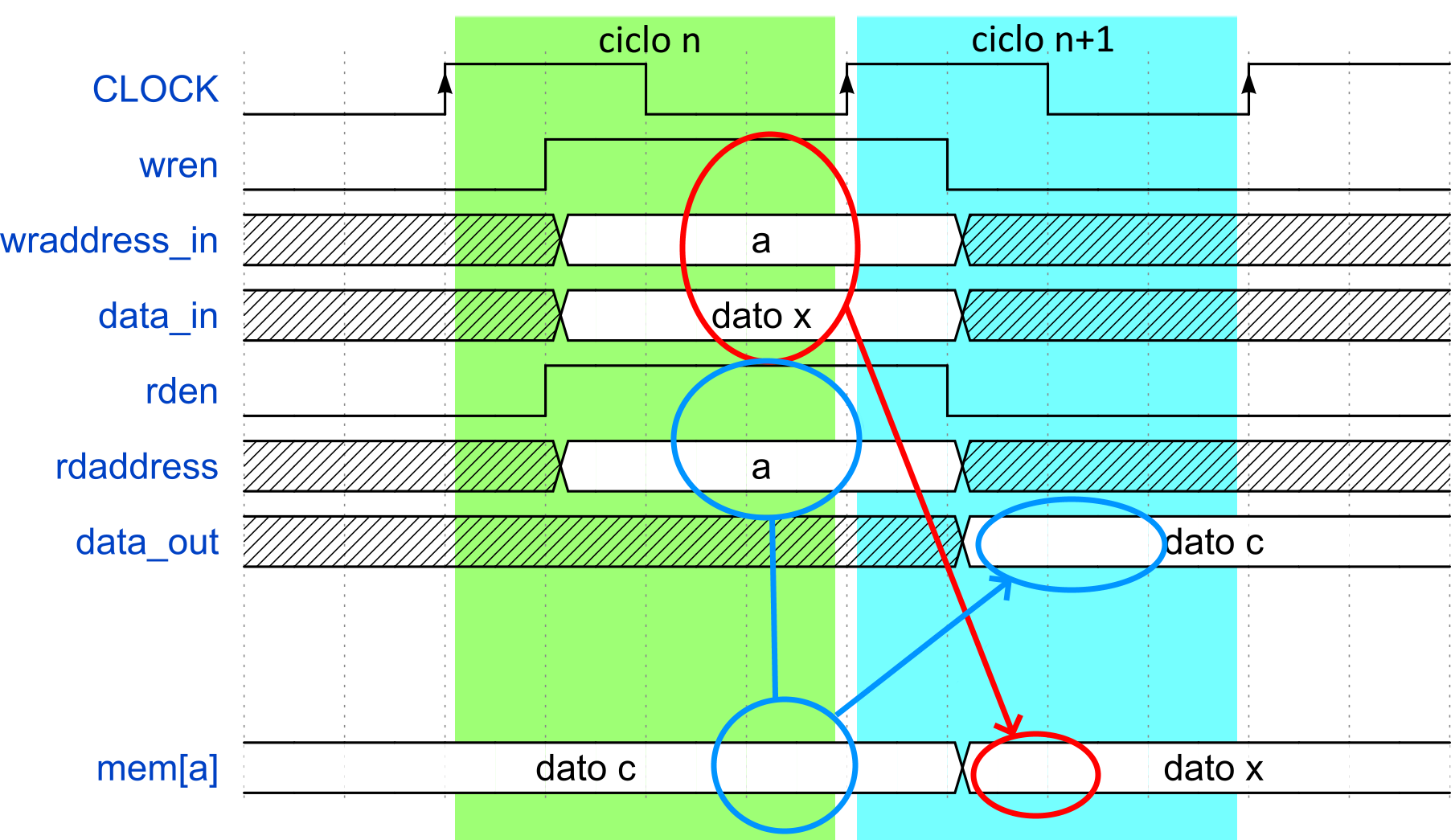

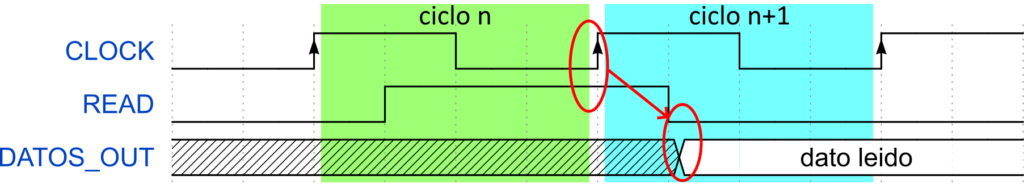

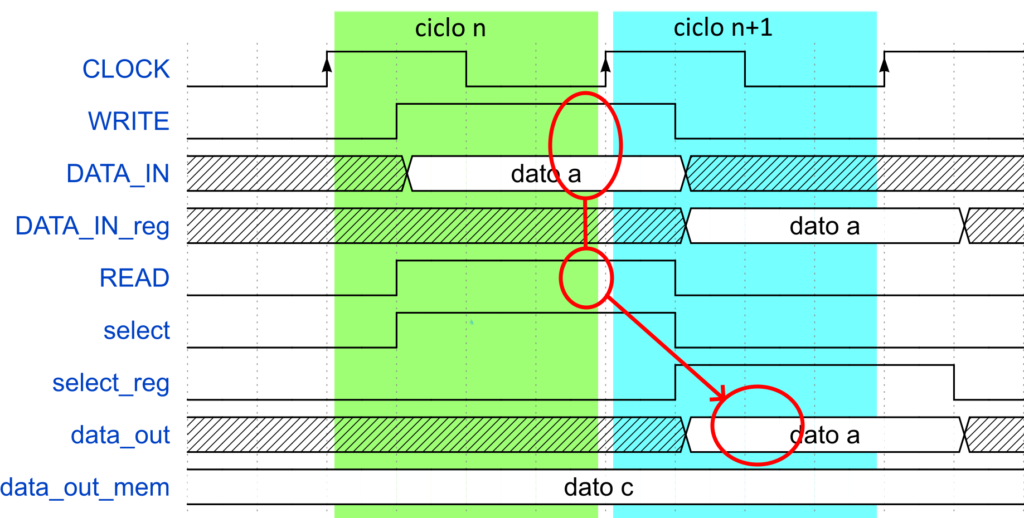

Como podemos ver en la imagen anterior, si queremos realizar una lectura de un dato, activamos la señal READ, esta señal es capturada por el flanco de reloj y su resultado, el dato leído, es obtenido después del flanco de reloj.

Hay que tener en cuenta que la activación de READ se produce en el ciclo de reloj n, pero los resultados leídos en DATA_OUT se producen en el ciclo de reloj n+1.

Lectura y escritura de una memoria RAM.

Analicemos que pasa con la escritura y lectura de una memoria RAM que tiene escritura síncrona y lectura síncrona.

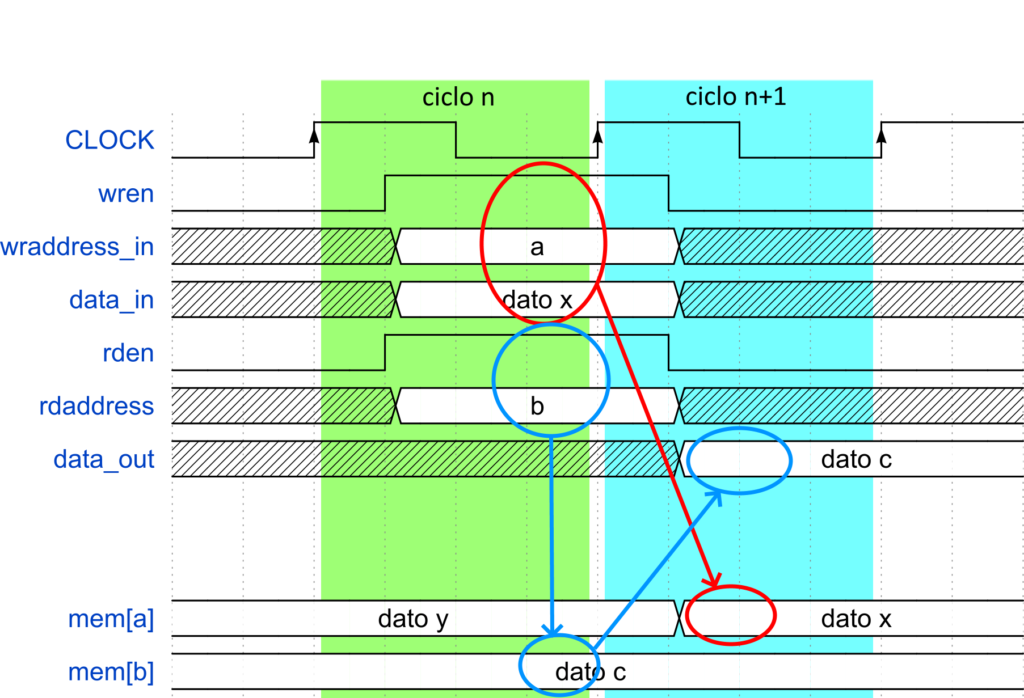

Veamos como se realiza una escritura en la posición “a” de la memoria y una lectura en la posición “b” de la memoria:

- Para escribir un dato “x” en la posición “a” de la memoria (marcado en rojo) tenemos que activar el wren, colocar la dirección “a” en wraddress y el dato “x” en data_in. Como es un sistema síncrono si esto lo hacemos en el ciclo n, el resultado estará guardado en memoria en el ciclo n+1.

- Para leer un dato almacenado en la posición “b” de la memoria (marcado en azul), tenemos que activar rden, colocar la dirección “b” en rdaddress. Como es un sistema síncrono si esto lo hacemos en el ciclo n, el resultado de lectura estará en data_out en el ciclo n+1.

Importante notar los tiempos del proceso, la escritura en la memoria se finaliza en el ciclo siguiente a la solicitud de escritura. La lectura de la memoria se hace efectiva en data_out en el ciclo siguiente a su solicitud.

Problemática de la escritura y lectura simultanea de la misma posición de memoria RAM.

Vamos a la problemática de la escritura y lectura simultanea de la misma posición de memoria. Esta problemática afectará a la lectura y escritura simultanea de una FIFO basada en este tipo de memoria cuando esta FIFO esté vacía.

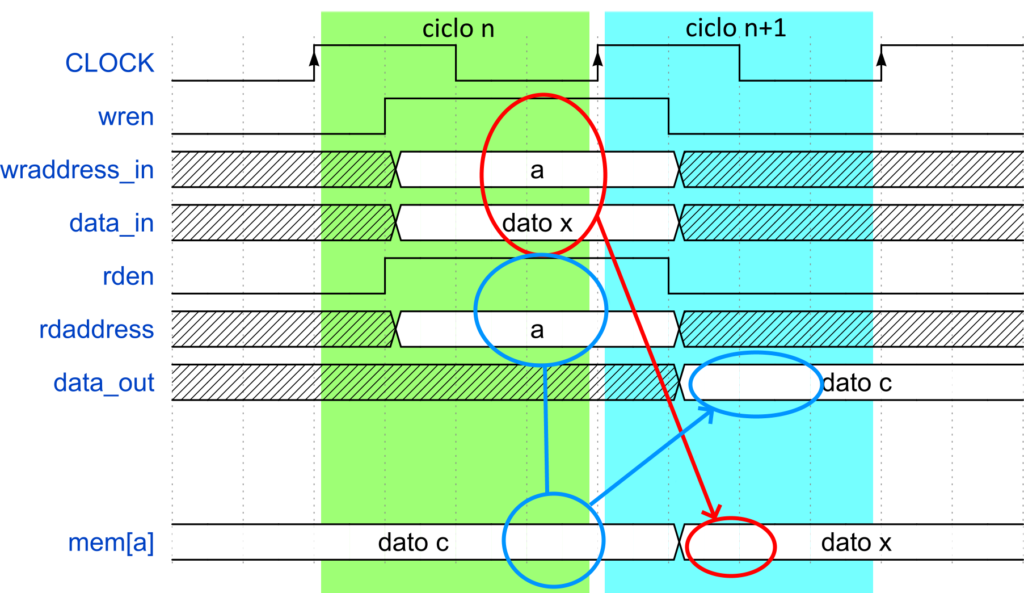

Veamos el ejemplo de escribir un dato x en la posición “a” de la memoria RAM y de manera simultanea leer el dato almacenado en la misma posición “a” de la memoria.

Si nos fijamos en la imagen anterior, el dato leído no es el nuevo dato escrito (dato x), si no el que teníamos anteriormente en la memoria (dato c). Esto se debe a que la escritura solicitada en el ciclo n, por la naturaleza secuencial del circuito, se realiza en el ciclo n+1.

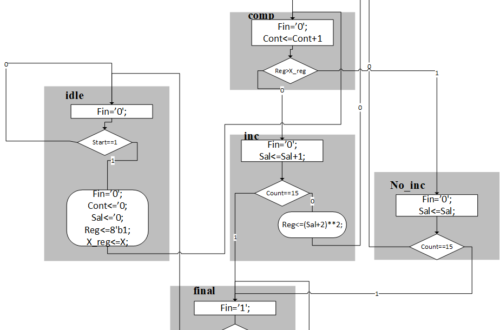

Lectura y Escritura simultanea de la FIFO VACÍA . Diseño de la etapa de salida.

Si implementamos la FIFO con esta memoria RAM, cuando se lee y escribe simultáneamente estando la FIFO vacía, no podemos hacer uso de la RAM. Tened en cuenta, que el dato leído en el ciclo n+1, en este caso particular, tiene que ser la entrada data_in en el ciclo n. Pero si ese data_in hay que escribirlo y leerlo de la RAM tardaríamos dos ciclos de reloj. Para resolver esto, tenemos que hacer un “bypass” de la RAM en esta situación particular.

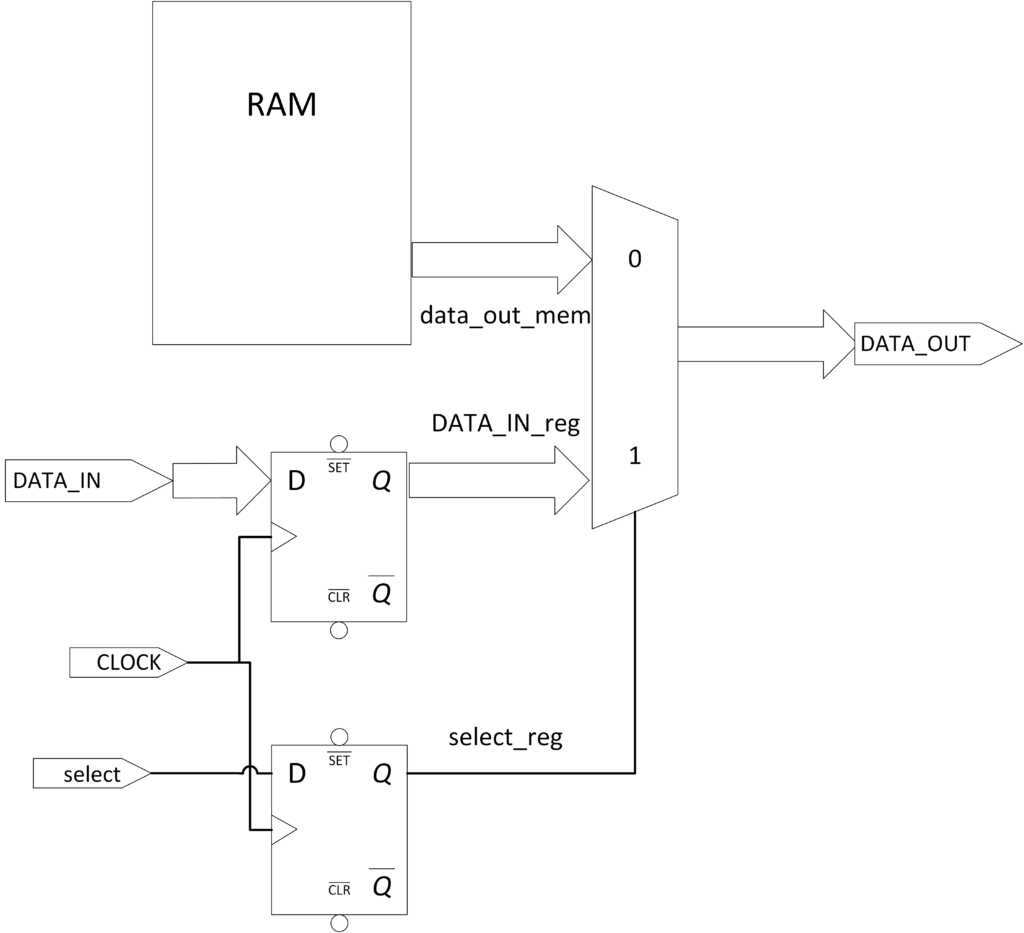

El circuito de salida de la FIFO propuesto para resolver el problema es el siguiente:

La salida de la FIFO será tomada normalmente de la RAM (data_out_mem) excepto en el caso particular de una lectura y escritura simultanea con fifo vacía. La máquina de estados detectará esa situación y activará una señal de salida select, que nos permitirá seleccionar la salida adecuada. Esta señal select se genera en el bloque combinacional de cálculo de salidas del máquina de estados. No debemos olvidar que la salida DATA_OUT es en el ciclo n+1, pero la solicitud de lectura en el ciclo n, por tanto, la entrada DATA_IN y la señal select deben ser registradas para puedan tener su efecto en el ciclo n+1

De esta forma la temporización de las señales para el caso particular de lectura y escritura simultanea en la FIFO cuando está VACÍA quedará como se indica a continuación:

Como nota final, cabe destacar que el valor de salida de la FIFO en DATA_OUT, será únicamente válido en el ciclo después de la solicitud de lectura.