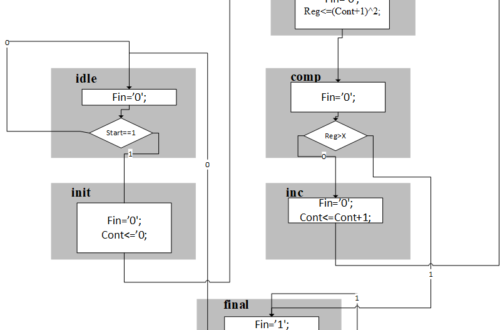

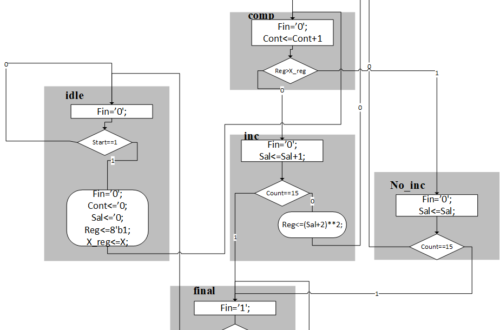

Paso 3: Realización de la segmentación

Partimos por tanto de la siguiente descripción. Nuestra intención es ahora hacer la segmentación de esta descripción algorítmica escrita en SystemVerilog.

module sed2(

CLK,

START,

RESET,

X,

FIN,

COUNT

);

input wire CLK;

input wire START;

input wire RESET;

input wire [7:0] X;

output logic FIN;

output logic [3:0] COUNT;

enum logic [2:0] {idle,comp,inc,No_inc,finali} state;

logic [3:0] Cont;

logic start;

logic [3:0] Sal;

logic [8:0] Reg;

logic [8:0] X_reg;

assign start=START;

always_ff @(posedge CLK, negedge RESET)

if (!RESET)

begin

Reg<='0;

Cont<='0;

Sal<='0;

X_reg<='0;

state<=idle;

end

else

case (state)

idle: if (start)

begin

Sal<='0;

Reg<=8'b1;

X_reg<=X;

Cont<='0;

state<=comp;

end

else

state<=idle;

comp:

begin

Cont<=Cont+1;

if (Reg>X)

state<=No_inc;

else

state<=inc;

end

inc:

begin

Sal<=Sal+1;

if (Cont==15)

state<=finali;

else

begin

Reg<=(Sal+2)**2;

state<=comp;

end

end

No_inc:

begin

Sal<=Sal;

if (Cont==15)

state<=finali;

else

state<=comp;

end

finali:

if (!start)

state<=idle;

else

state<=finali;

endcase

assign COUNT=Sal;

always_comb

case (state)

finali: FIN=1'b1;

default: FIN=1'b0;

endcase

endmoduleEl procedimineto de segmentación lo podemos observar en el siguiente vídeo

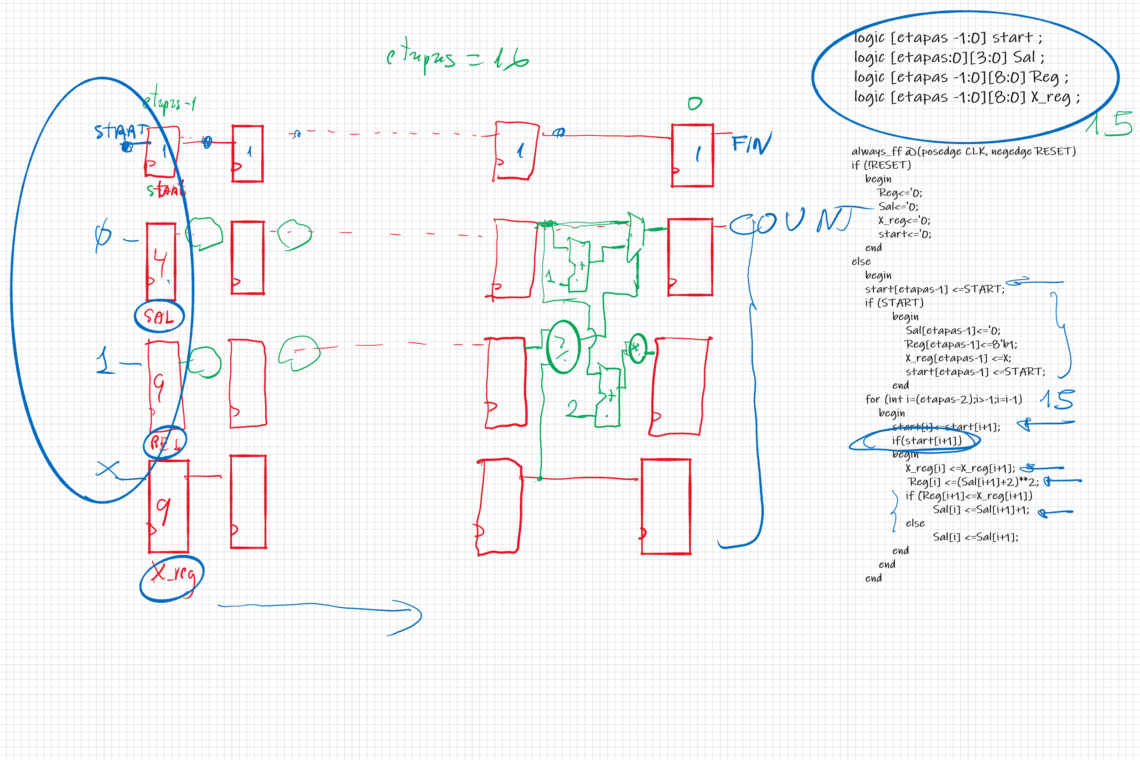

Mostramos ahora el resultado de nuestra segmentación:

module sed2_seg(

CLK,

START,

RESET,

X,

FIN,

COUNT

);

parameter tamano=4;

localparam etapas= 2**tamano;

input wire CLK;

input wire START;

input wire RESET;

input wire [7:0] X;

output logic FIN;

output logic [3:0] COUNT;

logic [etapas -1:0] start ;

logic [etapas -1:0][3:0] Sal ;

logic [etapas -1:0][8:0] Reg ;

logic [etapas -1:0][8:0] X_reg ;

always_ff @(posedge CLK, negedge RESET)

if (!RESET)

begin

Reg<='0;

Sal<='0;

X_reg<='0;

start<='0;

end

else

begin

start[etapas-1] <=START;

if (START)

begin

Sal[etapas-1]<='0;

Reg[etapas-1]<=8'b1;

X_reg[etapas-1] <=X;

start[etapas-1] <=START;

end

for (int i=(etapas-2);i>-1;i=i-1)

begin

start[i]<=start[i+1];

if(start[i+1])

begin

X_reg[i] <=X_reg[i+1];

Reg[i] <=(Sal[i+1]+2)**2;

if (Reg[i+1]<=X_reg[i+1])

Sal[i] <=Sal[i+1]+1;

else

Sal[i] <=Sal[i+1];

end

end

end

assign FIN=start[0];

assign COUNT=Sal[0];

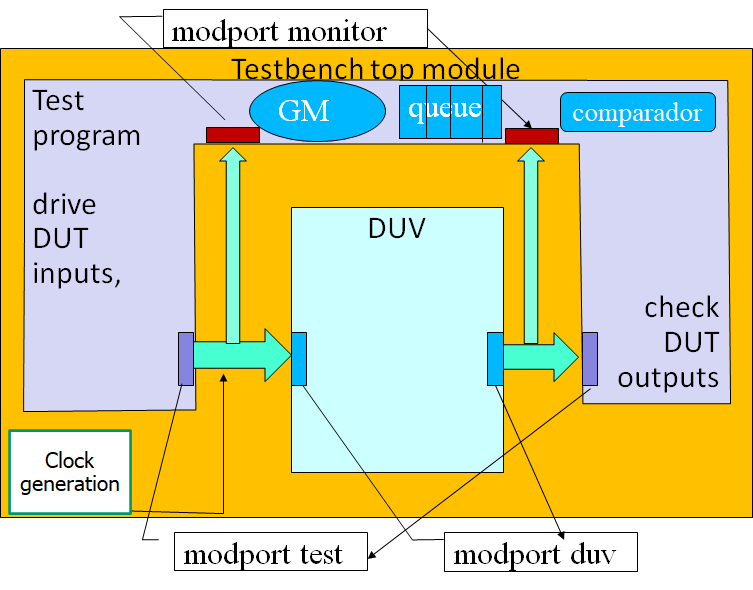

endmoduleVeamos ahora las prestaciones en área y velocidad conseguidas por esta segmentación realizada. De paso observaremos que nuestros bancos de verificación, si son lo suficientemente robustos, pueden adaptarse al diseño multiciclo original o a la solución pipeline final.