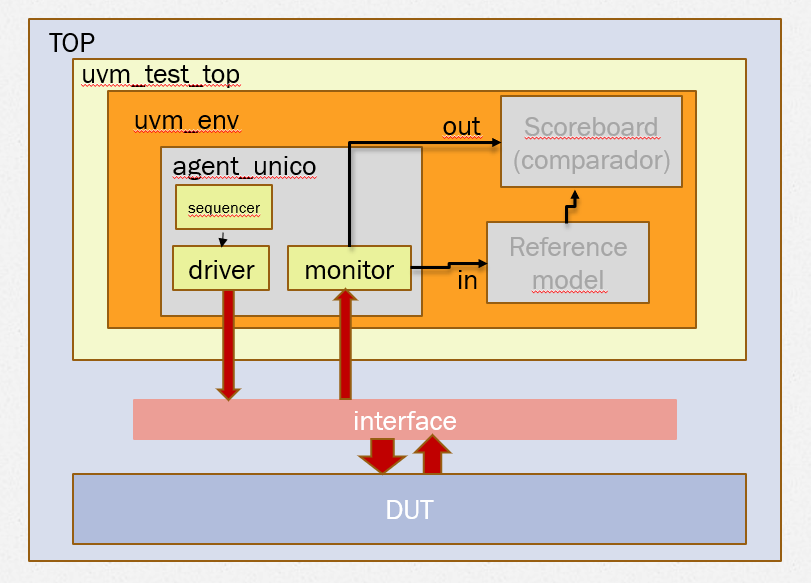

En esta sesión nos vamos a centrar en la creación del test de la siguiente figura (RECUADRO EN AMARILLO) y su posterior refinamiento, tanto de la generación de estímulos como en la observación de los resultados.

El esquema que vamos a seguir es el siguiente:

- Creación del test

- Inserción de un agente

- Generación del «enviroment»

- Generación del test. Esta generación de test a su vez requiere de:

- Generación de secuencia

- Generación de secuencia virtual

- Generación propiamente del test

- Generación de los estímulos y

- Observación de los resultados

Creación del test

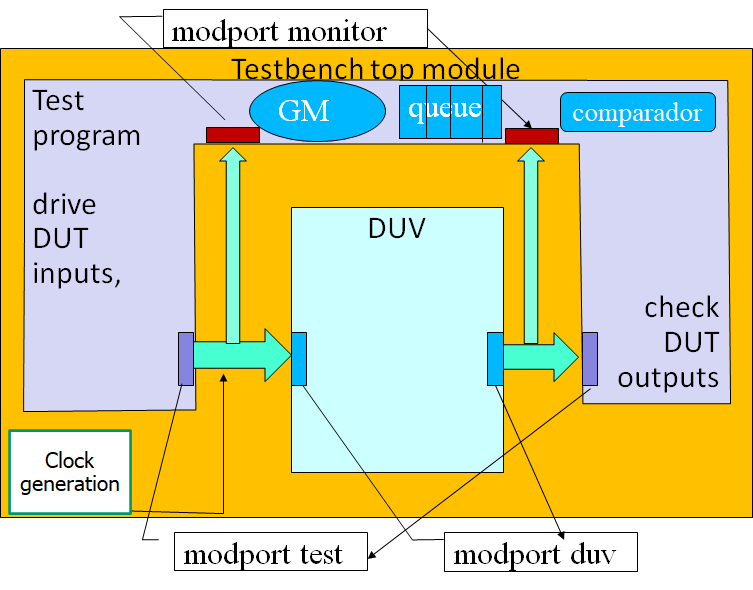

Como puede observarse por los pasos a seguir es una metodología «bottom-up». Antes de ello recapitularemos nuestros pasos de la primera sesión para adaptarlos definitivamente al diseño propuesto: Un divisor algorítmico, ya que nuestra estructura de dut y nuestro interfaz estaban extraídos de un diseño de otro circuito aritmético algorítmico: un radicador.

Adaptación al circuito divisor

Supongamos que ha habido un cambio en el diseño y en las especificaciones. ¿Qué deberíamos cambiar? ¿Qué permanecería sin cambios?

Empecemos con lo que no cambiaría:

- Podemos seguir trabajando con el mismo proyecto

- Podemos seguir trabajando con el TOP general definido en la sesión anterior (recuadro azul)

Nuestros cambios deberían centrarse en los bloques interfaz y DUT.

En cuanto a lo primero, el interfaz, teníamos un interfaz ejemplo que os proporcioné que servía para interfasar con un circuito aritmético con un solo operando de entrada y una solo resultado. Ahora tenemos dos operandos y dos resultados. Haced los cambios pertinentes si no los habéis hecho.

En cuanto al DUT, lo primero que tenemos básicamente es el diseño RTL (que como ingenieros de verificación se nos suele proporcionar) y un top_dut que os recuerdo hace la adaptación de puertos al interfaz que acabamos de adaptar.

Creación de la infraestructura test

Os proporciono el siguiente vídeo para que veáis como proceder con el ejemplo del radicador.

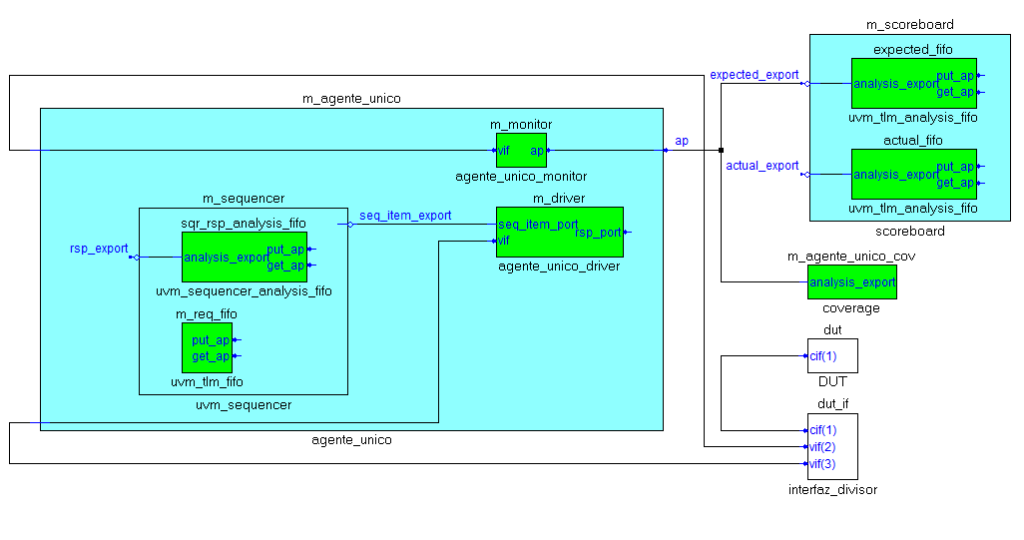

Fijaros que en este paso hemos tirado fundamentalmente de Templates proporcionados por el asistente y prácticamente lo que es el esqueleto de toda la estructura de test ya la tenemos realizada.

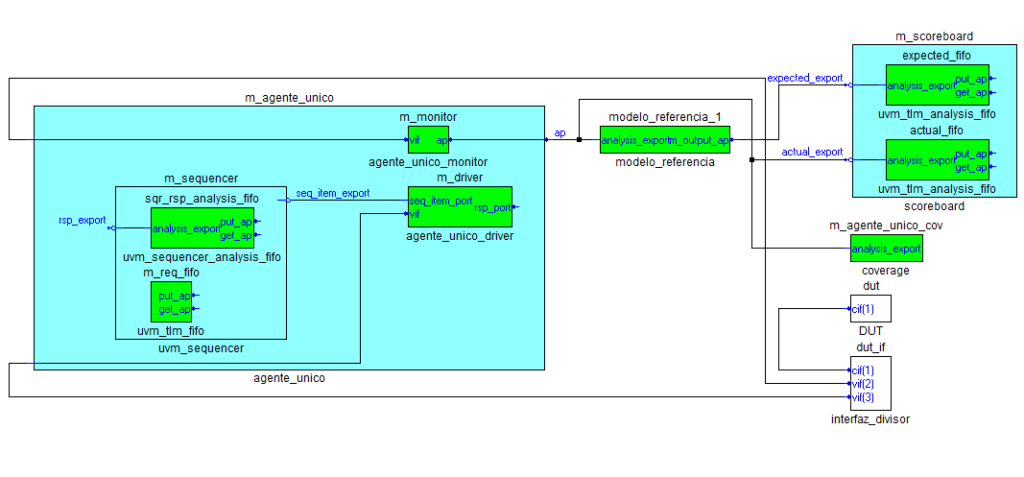

Si habéis seguido los pasos correctamente debe de apareceros una figura tal como la siguiente:

Generación de los estímulos

Vamos a introducir RCSG (Random Constraint Stimulus Generation) siguiendo los siguientes pasos:

- Secuencia-Test asociado a dicha secuencia

- “Item” del “agent”

- “Driver” del “agent”

Visto el procedimiento que hemos seguido proponemos tunear nuestra primera secuencia con los siguientes objetivos:

- Randomizar el numerador y el denominador

- Colocar un constraint de que el numerador sea positivo

- Colocar una constraint de que el denominador sea positivo

- hacer 50 repeticiones en dicha secuencia

- Monitorizar cuando el reset esté desactivo en todos los flancos de reloj siempre y cuando termina el algoritmo

- Compilar el diseño y estímulos generados y lanzar el simulador

Observación de resultados

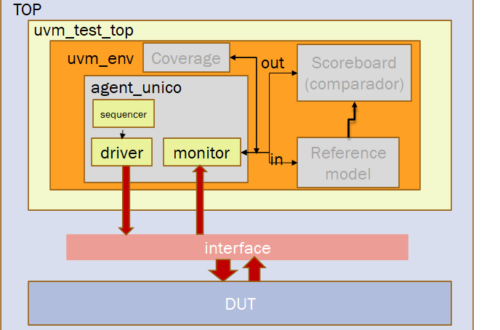

Vamos ahora a automatizar en la medida de lo posible la observación de resultados. Para ello fundamentalmente necesitamos (que aun tenemos pendiente) la introducción de un modelo de referencia (Golden model) y trazar un buen muestreo de las entradas y salidas de nuestra DUT para qe las entradas sean llevadas al modelo de referencia y las salidas sean llevadas al scorborad para comparar los resultados con el modelo de eferencia. Eso obliga por supuesto a que el modelo de referencia esté también perfectamente conectado al scoreboard.

El esquema de lo que nos queda por hacer es:

- Definición modelo de referencia

- Introducción del mismo en el «enviroment»

- Conexionado del modelo de referencia

- Procedimiento básico de monitorización

Recomendaciones finales

En el vídeo anterior quedan algunas cosas pendientes:

- Se define inserta y conecta el modelo de referencia pero no se concreta la realización del modelo de referencia. Evidentemente es un paso diseño dependiente. Si se quiere observar un ejemplo de refinamiento y descripción de un modelo de referencia para un radicador podéis observarlo en el primer punto del siguiente vídeo. La idea es saber ahora cómo hariais el modelo de referencia del divisor.

- El scoreboard generado por los templates requiere un ligero cambio para que refleje perfectamente el comportamiento del duv (comportamiento obtenido-actual) y el comportamiento del modelo de referencia ante los mismos estímulos (comportamiento esperado-expected). Estad muy atentos porque esos cambios están descritos el el anterior vídeo en el punto 3 de su esquema de desarrollo.

- Por último queda la determinación correcta del mónitor de vuestro agente. La monitorización determinada por el template establece unos flancos de reloj para hacer ese muestreo, presuponiendo que el reset esté desactivo (cuidado con el nivel de ese reset desactivo!), y con una supuesta señál de validación de las respuestas correctas. De nuevo necesitamos refinar este fichero y adaptarlo a la forma de operar del diseño objeto de verificación