Instrucciones iniciales

- Haremos las sesiones de este seminario en el aula informática I (situado en la planta baja del edificio 4D de la ETSIT

- Necesito que vayáis equipados con vuestro portátil y que tengáis instalado dos programas que teneis en recursos de poliformat. Son Questasim (que es posible que algunos de vosotros ya tengáis instalado) y un assistente de systemverilog denominado SystemVerilog-VHDL assistant. Afortunadamente no son programas muy pesados y para poder ejecutarlos necesitaréis estar en la VPN de la universidad (si estáis fuera de la universidad) o conectados a través de UPVNET. Es necesario que añadáis una variable de entorno a vuestro windows que encontraréis disponible bajo la carpeta de questasim de recursos del poliformat del curso de formación Aula de Microelectrónica.

- Para aquellos que no dispongan de esta infraestructura, intentaremos crear algún usuario en polilabs bajo demanda. Esta es una solución más lenta y que resolveremos al principio de la semana que viene . Es posible que muchos de vosotros (los alumnos MUISE) tengáis acceso a la máquina de polilabs denominada ETSIT-CADENCE2. En dicha máquina también están instalados los programas. Para su correcto funcionamiento os adjuntaré en recursos los ficheros a colocar en vuestro «home» para su correcto funcionamiento.

- Para terminar, mi canal de comunicación con vosotros será a partir de ahora será la página web https://dsd.webs.upv.es/ En dicha web está grabados en video los pasos que vamos a hacer en este seminario y que intentaré ejecutar en directo. Es muy importante que vengáis equipados con auriculares!!

Diseño a verificar

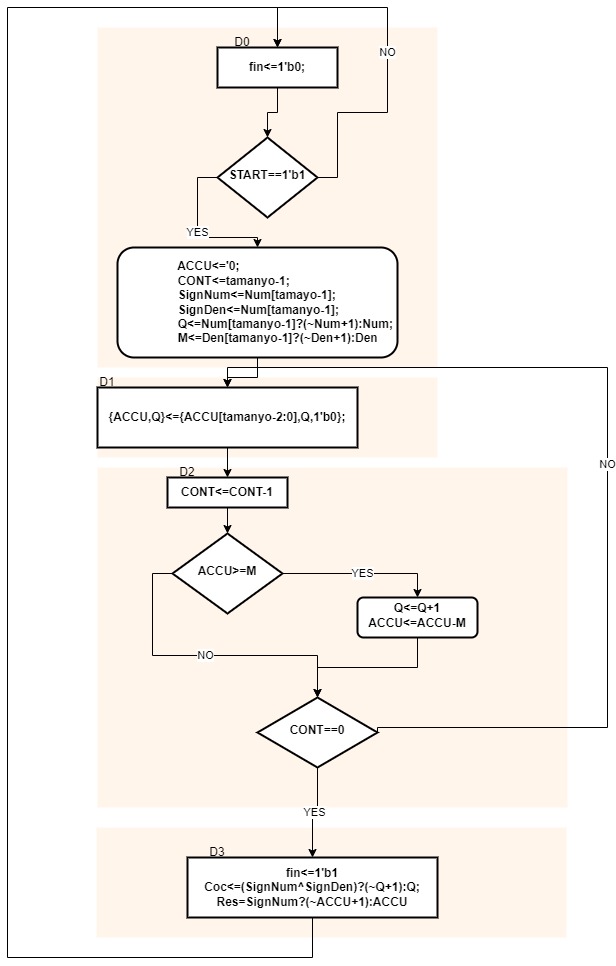

Vamos a verificar un divisor algorítmico. El código ASM es el que se adjunta en la siguiente figura

Os adjunto información de cómo deberían denominarse los puertos y de entrada y salida. Es muy importante respetar este tipo de nombres sobre todo si se quiere reusar un banco de pruebas previo.

Entity: Divisor_Alg2

- File: Divisor_Alg3.sv

Diagram

Generics

| Generic name | Type | Value | Description |

|---|---|---|---|

| tamanyo | 32 |

Ports

| Port name | Direction | Type | Description |

|---|---|---|---|

| CLK | input | ||

| RSTa | input | ||

| Start | input | ||

| Num | input | [tamanyo-1:0] | |

| Den | input | [tamanyo-1:0] | |

| Coc | output | [tamanyo-1:0] | |

| Res | output | [tamanyo-1:0] | |

| Done | output |

Signals

| Name | Type | Description |

|---|---|---|

| state1 | enum logic [2:0] { D0, D1, D2, D3} |

|

| ACCU | logic [tamanyo-1:0] | |

| M | logic [tamanyo-1:0] | |

| Q | logic [tamanyo-1:0] | |

| SignNum | logic | |

| SignDen | logic | |

| CONT | logic [size_cont-1 :0] | |

| fin | logic |

Constants

| Name | Type | Value | Description |

|---|---|---|---|

| size_cont | $clog2(tamanyo-1) |

Processes

- unnamed: ( @(posedge CLK or negedge RSTa) )

Type: always_ff

State machines

Comportamiento

El comportamiento es el mostrado en el siguiente cronograma

Procedimientos

En esta sesión nos vamos a conformar en la realización del diseño y del proyecto del systemverilog assistant donde importaremos dicho fichero para realizar en las siguientes sesiones la verificación

Diseño

Para la realización del diseño seguid las pautas del siguiente video en el cual el algoritmo realizado es un radicador. Con este procedimiento agilizaremos el diseño aunque no se vislumbre claramente los elementos del control-path y del data-path; pero también es importante que sepáis hacer ese traslado directo de ASM a systemVerilog.

Creacion del proyecto

Objetivos:

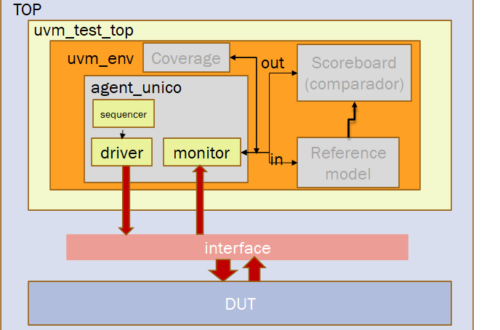

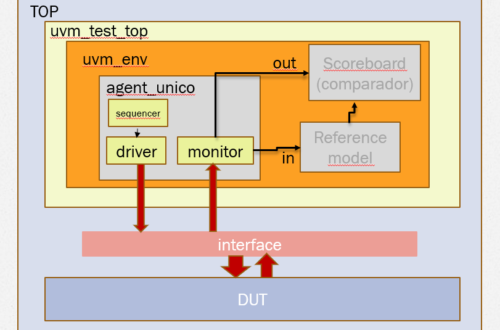

- Nuestro principal objetivo es la generación del proyecto de banco de pruebas basado en metodología UVM (Universal Verification Methodology)

Esquema

- Arranque de la herramienta asistente

- Creación del proyecto

- Importación de ficheros existentes (pertenecientes al diseño a verificar)

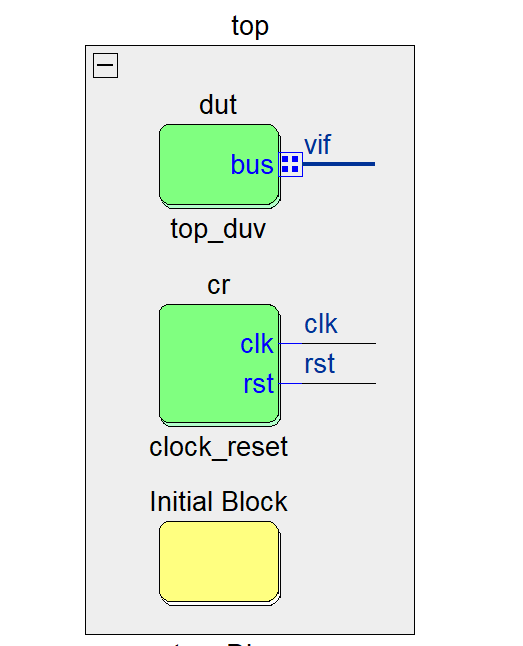

Creación del top

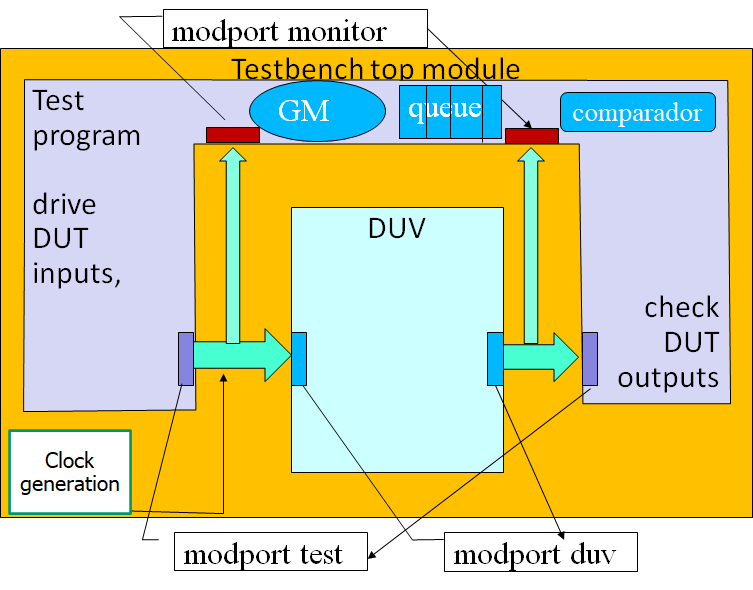

En el siguiente vídeo vamos a proponer el siguiente esquema

- Estructura del top propuesta

- Generación del interfaz

- Modificación del interfaz

Como punto de partida del interfaz y del encapsulamiento del DUT en el mismo os adjunto los ficheros correspondientes al ejemplo descrito en los vídeos.

INTERFAZ

`timescale 1ns/1ps

interface test_if ( input bit reloj, input bit rst) ;

logic empieza ;

logic termina ;

logic [7:0] data_in ;

logic [4:0] data_out;

clocking md @(posedge reloj);

input #1ns data_out;

input #1ns data_in;

input #1ns empieza;

input #1ns termina;

endclocking:md;

clocking sd @(posedge reloj);

input #2ns data_out;

output #2ns data_in;

input #2ns termina;

output #2ns empieza;

endclocking:sd;

modport monitor (clocking md);

modport test (clocking sd);

modport duv (

input reloj ,

input rst ,

output termina ,

input empieza ,

input data_in ,

output data_out

);

endinterfaceEste ejemplo de interfaz utiliza tres «mod ports» : dos de ellos para proporcionar dos puntos de vista que debe usar el test: control (color violeta) y observabilidad (color granate); y un tercer punto de vista que utilizará el DUT (color azul en la figura)

.

Los dos modos que usará el baco de pruebas UVM tienen asociados sus correspondientes «clocking blocks» para sincronizar esas comunicaciones.

La pregunta ahora sería: ¿cómo hacemos el interfaz para el divisor teniendo en cuenta que tenemos no solo un operando de entrada sino dos (Numerador y Denominador), y no solo un resultado sino dos (Cociente y Resto)?

Conexión DUT al interfaz

El framework de UVM del SystemVerilog tiende a realizar las conexiones de DUT con el interfaz de una manera específica. Yo os he propuesto en el vídeo realizar primero un encapsulamiento de vuestro DUT en un nivel jeráquico superior (que llamaremos top_dut o top_duv) . Mirad el ejemplo de cómo lo hacemos con el top del radicador.

module top_duv (interfaz_radicador bus) ;

sed radicador_duv(

.CLK (bus.clk), // Clock input

.RESET (bus.rst), // Active LOW ASINCRONOUS reset

.X (bus.data_in), // Data input

.COUNT (bus.data_out),// Data Output

.START (bus.empieza), // duv empieza

.FIN (bus.termina) //duv termina

);

endmoduleIgualmente partiendo de este ejemplo: ¿cómo hariais el caso del divisor?

Seguimiento

Sería ideal para empezar la segunda sesión (jueves 16 de junio) que tengáis un fichero systemverilog escrito del diseño a verificar, las herramientas perfectamente intaladas y el proyecto del asistente preparado.

En segundo término deberías ya haber escrito tu interfaz, haber adaptado tu DUT al mismo y haber creado el top mediante el framework utilizado de forma que nos quede una visualización de la misma como la que se adjunta en la siguiente figura