Paso 1: Realización ASM con un solo fichero

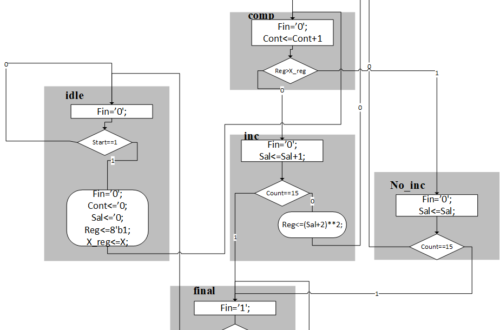

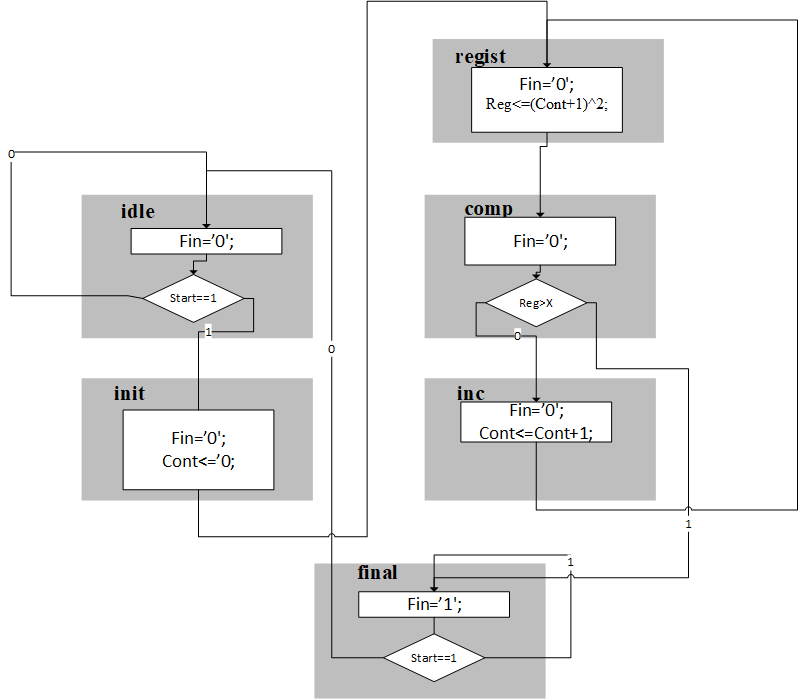

En esta entrada vamos a explicar cómo podemos describir directamente un ASM con un solo fichero. Este será nuestro primer paso para la consecución de una solución segmentada; pero nos va a servir para que podáis observar que el particionado Control-Path y Data-path puede ser acometido de forma diferente a como lo vamos haciendo en nuestras tareas.

En esta alternativa de diseño que ahora vamos a seguir, se procede a un nivel de abstracción superior. Eso quiere decir que no vamos a instanciar los subsistemas del data path para luego interconectarlos y controlarlos mediante señales de control diseñadas en nuestra FSM (control-path) ; sino que todos estos elementos van a ser inferidos a partir de un código systemverilog único bastante sencillo y sobre todo siendo reflejo directo de lo descrito en el ASM .

Ventajas:

- Más rápido de describir

- Mucho más fácil de describir por ser prácticamente el código ASM especificado

Desventajas:

- En diseños complejos donde los elementos del data-path pueden tener una cierta envergadura, inferirlos a través de código es mucho menos eficiente en área y velocidad que instanciando subsistemas óptimos realizados en vuestro centro de diseño.

- Es difícil de particionar puesto que prácticamente todo es descrito en un solo fichero. El reúso es muy minimizado

Vamos a utilizar el ejemplo del radicador

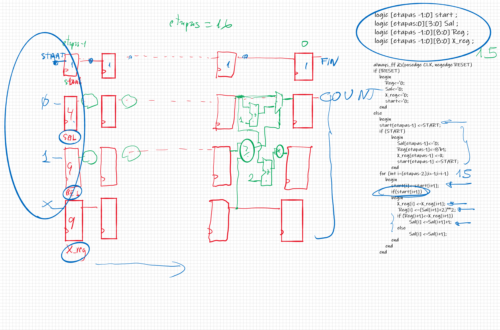

El código obtenido es:

module sed(

CLK,

START,

RESET,

X,

FIN,

COUNT

);

input wire CLK;

input wire START;

input wire RESET;

input wire [7:0] X;

output logic FIN;

output wire [3:0] COUNT;

enum logic [2:0] {idle,init,regist,comp,inc,finali} state;

logic [3:0] Cont;

logic [8:0] Reg;

assign COUNT=Cont;

always_ff @(posedge CLK, negedge RESET)

if (!RESET)

begin

Reg<='0;

Cont<='0;

state<=idle;

end

else

case (state)

idle: if (START)

state<=init;

else

state<=idle;

init:

begin

Cont<='0;

state<=regist;

end

regist:

begin

state<=comp;

Reg<=(Cont+1)**2;

end

comp:

if (Reg>X)

state<=finali;

else

state<=inc;

inc:

begin

Cont<=Cont+1;

state<=regist;

end

finali:

if (!START)

state<=idle;

else

state<=finali;

endcase

always_comb

case (state)

finali: FIN=1'b1;

default: FIN=1'b0;

endcase

endmodule