El planteamiento de esta entrada es si podemos hacer una verificación física del RISC-V, en la placa DE2-115 mediante el LCD. La controladora verilog de LCD proviene de la siguiente dirección y autoría: https://gist.github.com/windhooked/40f6c9a6d35062a5d24503d2bcb07ddd La adaptación que he realizado ha consistido fundamentalmente en generar una salida adicional que resetee el micro RISC-V mientras el LCD arranca, de forma que cuando…

-

-

Uso de aserciones en microprocesadores

Voy a plantear una utilidad de las aserciones concurrentes para verificación del buen hacer de vuestros diseños de microprocesadores, sobre todo ahora que estáis uniendo vuestro bloques funcionales del single-cycle. Supongamos que teneis un core cómo el que ahora os describo Pensad que posiblemente dentro del DATA_PATH tengáis el banco de registros con un nombre de instanciación RF1, y supongamos…

-

RCSG y cobertura funcional en microprocesadores

He creado esta entrada para que pensemos cómo podemos utilizar RCSG y covergroups en la verificación de un microprocesador. Una forma que se me ocurre de hacerlo (y desde luego no es única) es la que os voy a describir. Es el momento adecuado porque empezamos esta semana a conocer el código máquina de los diferentes tipos de instrucciones del…

-

Verificación hardware de un microprocesador simple

Con este ejemplo queremos mostrar algunas características que puedan ser útiles en el diseño de sistemas más complejos; pero la arquitectura de este microprocesador (Multi-Cycle Processor) tiene poco que ver con las solicitadas en la tarea 3 fase 2 (single cycle processor) y 3 (pipeline processor) : Realización de un interfaz para modelar un bus triestado de interconexión de los…

-

Banco de pruebas radicador

Siguiendo los pasos de la creación de un banco de pruebas para el radicador que responda a una estructura más actual y basada en systemVerilog, hemos visto conveniente hacer unas últimas incorporaciones que os puedan ayudar a mejorar el estilo de vuestros bancos de pruebas. Empecemos recordando la estructura que deseamos Estructura del banco de pruebas SystemVerilog En esta estructura…

-

Funcionamiento de clocking blocks

Vamos a poner un ejemplo de clocking block insertado dentro de un modulo Driver Si analizamos la generación de la secuencia de sd.dout (25=>33) podemos observar el efecto del clocking block en la copia exacta que tenemos en la señal dout retrasada un tiempo exactamente igual al skew especificado en la línea 8 Muestreo En cuanto a din (que es…

-

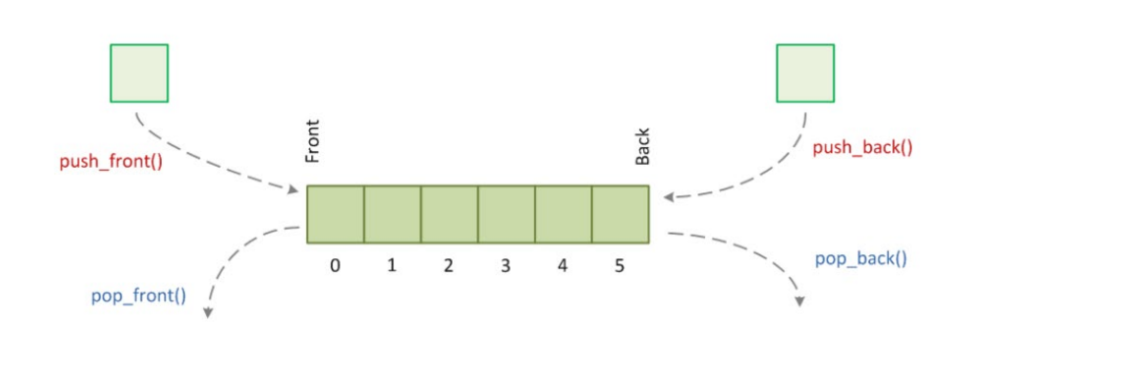

Modelo de Fifo ideal con colas

En este enlace podréis ver una modelización de una fifo como la solicitada en la tarea 1 mediante una cola y un pequeño banco de pruebas de algunos casos de verificación. Paso de argumentos por referencia siempre teniendo en cuenta que el paso no puede ser por valor sino por referencia (por eso se utiliza la palabra reservada ref). Si…

-

Simulación básica con colas